-b 1-1

```

@@ -330,7 +371,7 @@ When this project is updated, you can update the firmware over the air.

Visit the following website for OTA operations: [online OTA](http://corsacota.surge.sh/?address=dap.local:3241)

-For most ESP8266 devices, you don't need to care about flash size. However, improper setting of the flash size may cause the OTA to fail. In this case, please change the flash size with `idf.py menuconfig`, or modify `sdkconfig`:

+For most devices, you don't need to care about flash size. However, improper setting of the flash size may cause the OTA to fail. In this case, please change the flash size with `idf.py menuconfig`, or modify `sdkconfig`:

```

# Choose a flash size.

@@ -378,7 +419,7 @@ Recv data <- TCP <- Uart Rx <- external devices

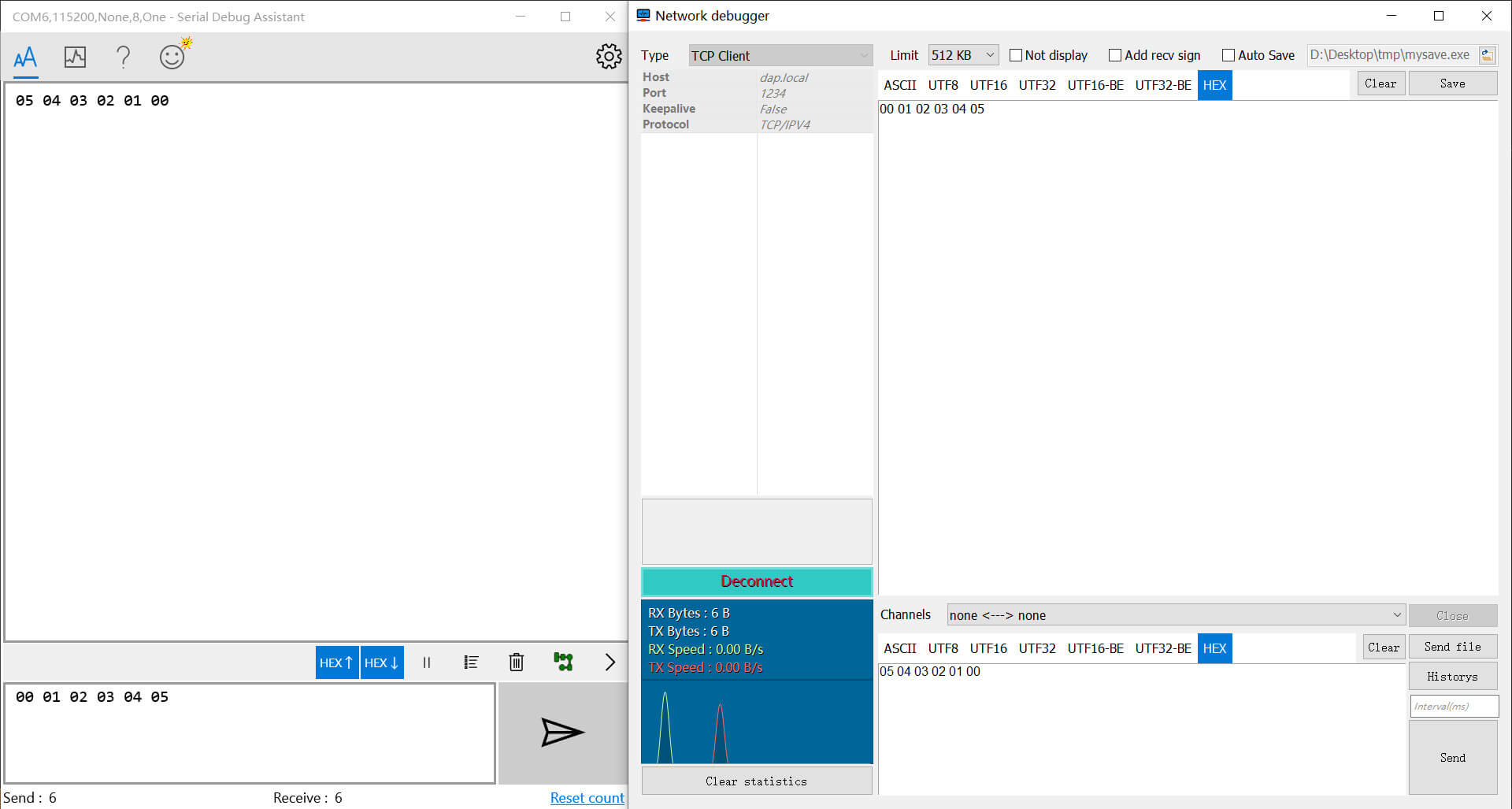

-When the TCP connection is established, bridge will try to resolve the text sent for the first time. When the text is a valid baud rate, bridge will switch to it.

+When the TCP connection is established, bridge will try to resolve the text sent for the first packet. When the text is a valid baud rate, bridge will switch to it.

For example, sending the ASCII text `115200` will switch the baud rate to 115200.

diff --git a/README_CN.md b/README_CN.md

index 6a68fbc..04461c6 100644

--- a/README_CN.md

+++ b/README_CN.md

@@ -1,3 +1,5 @@

+请注意:不同语言版本的翻译可能落后于项目的原始文档。请以原始文档为准。

+

diff --git a/components/DAP/config/DAP_config.h b/components/DAP/config/DAP_config.h

index 8b0e4cb..f8c909c 100644

--- a/components/DAP/config/DAP_config.h

+++ b/components/DAP/config/DAP_config.h

@@ -59,6 +59,7 @@

#include "esp8266/include/esp8266/gpio_struct.h"

#include "esp8266/pin_mux_register.h"

#elif defined CONFIG_IDF_TARGET_ESP32

+#elif defined CONFIG_IDF_TARGET_ESP32C3

#else

#error unknown hardware

#endif

@@ -95,6 +96,9 @@ This information includes:

#elif defined CONFIG_IDF_TARGET_ESP32

#define CPU_CLOCK 240000000

// <<<<<<<<<<<<<<<<<<<<<<<<<<<<<240MHz

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define CPU_CLOCK 16000000

+ // <<<<<<<<<<<<<<<<<<<<<<<<<<<<<160MHz

#endif

@@ -230,22 +234,32 @@ __STATIC_INLINE uint8_t DAP_GetSerNumString(char *str)

#define PIN_TDI 4

#define PIN_nTRST 0 // optional

#define PIN_nRESET 5

- // LED_BUILTIN

- #define PIN_LED_CONNECTED 2

- // LED_BUILTIN

+

+ #define PIN_LED_CONNECTED _ // won't be used

#define PIN_LED_RUNNING _ // won't be used

#elif defined CONFIG_IDF_TARGET_ESP32

#define PIN_SWDIO 12 // SPI MISO

#define PIN_SWDIO_MOSI 13 // SPI MOSI

#define PIN_SWCLK 14

- #define PIN_TDO 19 // device TDO -> Host Data Input ~~~(use RTC pin 16)~~~

+ #define PIN_TDO 19 // device TDO -> Host Data Input

#define PIN_TDI 18

#define PIN_nTRST 25 // optional

#define PIN_nRESET 26

- // LED_BUILTIN

- #define PIN_LED_CONNECTED 27

- // LED_BUILTIN

+

+ #define PIN_LED_CONNECTED _ // won't be used

#define PIN_LED_RUNNING _ // won't be used

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define PIN_SWDIO _ // SPI MISO

+ #define PIN_SWDIO_MOSI 7 // SPI MOSI

+ #define PIN_SWCLK 6

+ #define PIN_TDO 8 // device TDO -> Host Data Input

+ #define PIN_TDI 9

+ #define PIN_nTRST 4 // optional

+ #define PIN_nRESET 5

+

+ #define PIN_LED_CONNECTED _ // won't be used

+ #define PIN_LED_RUNNING _ // won't be used

+

#endif

@@ -380,6 +394,36 @@ __STATIC_INLINE void PORT_JTAG_SETUP(void)

GPIO_PULL_UP_ONLY_SET(PIN_nTRST);

GPIO_PULL_UP_ONLY_SET(PIN_nRESET);

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_INLINE void PORT_JTAG_SETUP(void)

+{

+ // set TCK, TMS pin

+

+

+ // PIN_TDO output disable

+ GPIO.enable_w1tc.enable_w1tc = (0x1 << PIN_TDO);

+ // PIN_TDO input enable

+ PIN_INPUT_ENABLE(GPIO_PIN_MUX_REG[PIN_TDO]);

+

+

+

+ // gpio_set_direction(PIN_TDI, GPIO_MODE_OUTPUT);

+ GPIO.enable_w1ts.enable_w1ts = (0x1 << PIN_TDI);

+ GPIO.pin[PIN_TDI].pad_driver = 0;

+ REG_CLR_BIT(GPIO_PIN_MUX_REG[PIN_TDI], FUN_PD); // disable pull down

+

+ // gpio_set_direction(PIN_nTRST, GPIO_MODE_OUTPUT_OD);

+ // gpio_set_direction(PIN_nRESET, GPIO_MODE_OUTPUT_OD);

+ GPIO.enable_w1tc.enable_w1tc = (0x1 << PIN_nTRST);

+ GPIO.pin[PIN_nTRST].pad_driver = 1;

+ GPIO.enable_w1tc.enable_w1tc = (0x1 << PIN_nRESET);

+ GPIO.pin[PIN_nRESET].pad_driver = 1;

+

+ // gpio_set_pull_mode(PIN_nTRST, GPIO_PULLUP_ONLY);

+ // gpio_set_pull_mode(PIN_nRESET, GPIO_PULLUP_ONLY);

+ GPIO_PULL_UP_ONLY_SET(PIN_nTRST);

+ GPIO_PULL_UP_ONLY_SET(PIN_nRESET);

+}

#endif

/**

@@ -430,7 +474,7 @@ __STATIC_FORCEINLINE uint32_t PIN_SWCLK_TCK_IN(void)

*/

__STATIC_FORCEINLINE void PIN_SWCLK_TCK_SET(void)

{

- GPIO.out_w1ts |= (0x1 << PIN_SWCLK);

+ GPIO_SET_LEVEL_HIGH(PIN_SWCLK);

}

/**

@@ -440,7 +484,7 @@ __STATIC_FORCEINLINE void PIN_SWCLK_TCK_SET(void)

*/

__STATIC_FORCEINLINE void PIN_SWCLK_TCK_CLR(void)

{

- GPIO.out_w1tc |= (0x1 << PIN_SWCLK);

+ GPIO_SET_LEVEL_LOW(PIN_SWCLK);

}

// SWDIO/TMS Pin I/O --------------------------------------

@@ -453,7 +497,7 @@ __STATIC_FORCEINLINE void PIN_SWCLK_TCK_CLR(void)

__STATIC_FORCEINLINE uint32_t PIN_SWDIO_TMS_IN(void)

{

// Note that we only use mosi in GPIO mode

- return ((GPIO.in >> PIN_SWDIO_MOSI) & 0x1) ? 1 : 0;

+ return GPIO_GET_LEVEL(PIN_SWDIO_MOSI);

}

/**

@@ -463,7 +507,7 @@ __STATIC_FORCEINLINE uint32_t PIN_SWDIO_TMS_IN(void)

*/

__STATIC_FORCEINLINE void PIN_SWDIO_TMS_SET(void)

{

- GPIO.out_w1ts |= (0x1 << PIN_SWDIO_MOSI);

+ GPIO_SET_LEVEL_HIGH(PIN_SWDIO_MOSI);

}

/**

@@ -473,7 +517,7 @@ __STATIC_FORCEINLINE void PIN_SWDIO_TMS_SET(void)

*/

__STATIC_FORCEINLINE void PIN_SWDIO_TMS_CLR(void)

{

- GPIO.out_w1tc |= (0x1 << PIN_SWDIO_MOSI);

+ GPIO_SET_LEVEL_LOW(PIN_SWDIO_MOSI);

}

/**

@@ -484,7 +528,7 @@ __STATIC_FORCEINLINE void PIN_SWDIO_TMS_CLR(void)

__STATIC_FORCEINLINE uint32_t PIN_SWDIO_IN(void)

{

// Note that we only use mosi in GPIO mode

- return ((GPIO.in >> PIN_SWDIO_MOSI) & 0x1) ? 1 : 0;

+ return GPIO_GET_LEVEL(PIN_SWDIO_MOSI);

}

/**

@@ -503,13 +547,13 @@ __STATIC_FORCEINLINE void PIN_SWDIO_OUT(uint32_t bit)

if ((bit & 1U) == 1)

{

//set bit

- GPIO.out_w1ts |= (0x1 << PIN_SWDIO_MOSI);

+ GPIO_SET_LEVEL_HIGH(PIN_SWDIO_MOSI);

}

else

{

//reset bit

- GPIO.out_w1tc |= (0x1 << PIN_SWDIO_MOSI);

+ GPIO_SET_LEVEL_LOW(PIN_SWDIO_MOSI);

}

}

@@ -546,6 +590,10 @@ __STATIC_FORCEINLINE void PIN_SWDIO_OUT_DISABLE(void)

// Note that the input of esp32 is not always connected.

PIN_INPUT_ENABLE(GPIO_PIN_MUX_REG[PIN_SWDIO_MOSI]);

GPIO.out_w1ts = (0x1 << PIN_SWDIO_MOSI);

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ // Note that the input of esp32c3 is not always connected.

+ PIN_INPUT_ENABLE(GPIO_PIN_MUX_REG[PIN_SWDIO_MOSI]);

+ GPIO.out_w1ts.out_w1ts = (0x1 << PIN_SWDIO_MOSI);

#endif

}

@@ -558,7 +606,7 @@ __STATIC_FORCEINLINE void PIN_SWDIO_OUT_DISABLE(void)

*/

__STATIC_FORCEINLINE uint32_t PIN_TDI_IN(void)

{

- return ((GPIO.in >> PIN_TDI) & 0x1) ? 1 : 0;

+ return GPIO_GET_LEVEL(PIN_TDI);

}

/**

@@ -572,14 +620,12 @@ __STATIC_FORCEINLINE void PIN_TDI_OUT(uint32_t bit)

if ((bit & 1U) == 1)

{

//set bit

- GPIO.out_w1ts |= (0x1 << PIN_TDI);

-

+ GPIO_SET_LEVEL_HIGH(PIN_TDI);

}

else

{

//reset bit

- GPIO.out_w1tc |= (0x1 << PIN_TDI);

-

+ GPIO_SET_LEVEL_LOW(PIN_TDI);

}

}

@@ -596,6 +642,8 @@ __STATIC_FORCEINLINE uint32_t PIN_TDO_IN(void)

return READ_PERI_REG(RTC_GPIO_IN_DATA) & 0x1;

#elif defined CONFIG_IDF_TARGET_ESP32

return ((GPIO.in >> PIN_TDO) & 0x1) ? 1 : 0;

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ return GPIO_GET_LEVEL(PIN_TDO);

#endif

}

@@ -633,7 +681,7 @@ __STATIC_FORCEINLINE void PIN_nTRST_OUT(uint32_t bit)

*/

__STATIC_FORCEINLINE uint32_t PIN_nRESET_IN(void)

{

- return ((GPIO.in >> PIN_nRESET) & 0x1) ? 1 : 0;

+ return GPIO_GET_LEVEL(PIN_nRESET);

}

/**

@@ -650,12 +698,12 @@ __STATIC_FORCEINLINE void PIN_nRESET_OUT(uint32_t bit)

if ((bit & 1U) == 1)

{

//set bit

- GPIO.out_w1ts |= (0x1 << PIN_nRESET);

+ GPIO_SET_LEVEL_HIGH(PIN_nRESET);

}

else

{

//reset bit

- GPIO.out_w1tc |= (0x1 << PIN_nRESET);

+ GPIO_SET_LEVEL_LOW(PIN_nRESET);

}

}

@@ -689,18 +737,7 @@ It is recommended to provide the following LEDs for status indication:

*/

__STATIC_INLINE void LED_CONNECTED_OUT(uint32_t bit)

{

-#if (!defined USE_UART_BRIDGE || USE_UART_BRIDGE == 0)

- if (bit)

- {

- //set bit

- GPIO.out_w1ts |= (0x1 << PIN_LED_CONNECTED);

- }

- else

- {

- //reset bit

- GPIO.out_w1tc |= (0x1 << PIN_LED_CONNECTED);

- }

-#endif

+ (void)(bit);

}

/**

@@ -712,6 +749,7 @@ __STATIC_INLINE void LED_CONNECTED_OUT(uint32_t bit)

*/

__STATIC_INLINE void LED_RUNNING_OUT(uint32_t bit)

{

+ (void)(bit);

// if (bit)

// {

// //set bit

@@ -774,20 +812,16 @@ __STATIC_INLINE void DAP_SETUP(void)

GPIO_FUNCTION_SET(PIN_TDI);

GPIO_FUNCTION_SET(PIN_nTRST);

GPIO_FUNCTION_SET(PIN_nRESET);

-#if (!defined USE_UART_BRIDGE || USE_UART_BRIDGE == 0)

- GPIO_FUNCTION_SET(PIN_LED_CONNECTED);

-#endif

+

// GPIO_FUNCTION_SET(PIN_LED_RUNNING);

// Configure: LED as output (turned off)

-#if (!defined USE_UART_BRIDGE || USE_UART_BRIDGE == 0)

- GPIO_SET_DIRECTION_NORMAL_OUT(PIN_LED_CONNECTED);

-#endif

+

// GPIO_SET_DIRECTION_NORMAL_OUT(PIN_LED_RUNNING);

- LED_CONNECTED_OUT(0);

- LED_RUNNING_OUT(0);

+ // LED_CONNECTED_OUT(0);

+ // LED_RUNNING_OUT(0);

PORT_OFF();

}

diff --git a/components/DAP/include/DAP.h b/components/DAP/include/DAP.h

index a011a92..cad17b3 100644

--- a/components/DAP/include/DAP.h

+++ b/components/DAP/include/DAP.h

@@ -296,14 +296,15 @@ extern void DAP_Setup (void);

#define USE_ASSEMBLY 1

#if (USE_ASSEMBLY == 0)

- __STATIC_FORCEINLINE void PIN_DELAY_SLOW(uint32_t delay)

+ __STATIC_FORCEINLINE void PIN_DELAY_SLOW(int32_t delay)

{

- uint32_t count = delay;

+ int32_t count = delay;

while (--count)

;

}

#else

-__STATIC_FORCEINLINE void PIN_DELAY_SLOW(uint32_t delay)

+ #if defined CONFIG_IDF_TARGET_ESP8266 || CONFIG_IDF_TARGET_ESP32

+__STATIC_FORCEINLINE void PIN_DELAY_SLOW(int32_t delay)

{

__asm__ volatile(

"l_PINDELAYSLOW%=:"

@@ -311,6 +312,16 @@ __STATIC_FORCEINLINE void PIN_DELAY_SLOW(uint32_t delay)

"BNEZ %[time], l_PINDELAYSLOW%=;"

: [time] "+r"(delay));

}

+ #elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_FORCEINLINE void PIN_DELAY_SLOW(int32_t delay)

+{

+ __asm__ volatile(

+ "l_PINDELAYSLOW%=:"

+ "ADDI %[time], %[time], -1;"

+ "BNEZ %[time], l_PINDELAYSLOW%=;"

+ : [time] "+r"(delay));

+}

+ #endif

#endif

diff --git a/components/DAP/include/gpio_common.h b/components/DAP/include/gpio_common.h

index ae77677..d7db811 100644

--- a/components/DAP/include/gpio_common.h

+++ b/components/DAP/include/gpio_common.h

@@ -28,6 +28,17 @@

#include "soc/soc/esp32/include/soc/spi_reg.h"

#endif

#include "hal/gpio_types.h"

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #include "soc/esp32c3/include/soc/gpio_struct.h"

+ #include "hal/esp32c3/include/hal/gpio_ll.h"

+ #include "hal/esp32c3/include/hal/clk_gate_ll.h"

+ #include "soc/esp32c3/include/soc/gpio_struct.h"

+ #include "soc/esp32c3/include/soc/dport_access.h"

+ #include "soc/esp32c3/include/soc/periph_defs.h"

+ #include "soc/esp32c3/include/soc/usb_serial_jtag_reg.h"

+ #include "soc/esp32c3/include/soc/io_mux_reg.h"

+ #include "soc/esp32c3/include/soc/spi_struct.h"

+ #include "soc/esp32c3/include/soc/spi_reg.h"

#else

#error unknown hardware

#endif

diff --git a/components/DAP/include/gpio_op.h b/components/DAP/include/gpio_op.h

index 8389972..3cfe2b6 100644

--- a/components/DAP/include/gpio_op.h

+++ b/components/DAP/include/gpio_op.h

@@ -44,8 +44,18 @@ __STATIC_INLINE __UNUSED void GPIO_FUNCTION_SET(int io_num)

// Note that the index starts at 0, so we are using function 3.

PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[io_num], PIN_FUNC_GPIO);

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_INLINE __UNUSED void GPIO_FUNCTION_SET(int io_num)

+{

+ // Disable USB Serial JTAG if pins 18 or pins 19 needs to select an IOMUX function

+ if (io_num == IO_MUX_GPIO18_REG || io_num == IO_MUX_GPIO19_REG) {

+ CLEAR_PERI_REG_MASK(USB_SERIAL_JTAG_CONF0_REG, USB_SERIAL_JTAG_USB_PAD_ENABLE);

+ }

+ PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[io_num], PIN_FUNC_GPIO);

+}

#endif

+

#ifdef CONFIG_IDF_TARGET_ESP8266

__STATIC_INLINE __UNUSED void GPIO_SET_DIRECTION_NORMAL_OUT(int io_num)

{

@@ -60,18 +70,54 @@ __STATIC_INLINE __UNUSED void GPIO_SET_DIRECTION_NORMAL_OUT(int io_num)

// PP out

GPIO.pin[io_num].pad_driver = 0;

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_INLINE __UNUSED void GPIO_SET_DIRECTION_NORMAL_OUT(int io_num)

+{

+ GPIO.enable_w1ts.enable_w1ts = (0x1 << io_num);

+ // PP out

+ GPIO.pin[io_num].pad_driver = 0;

+}

+#endif

+

+

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

+__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_HIGH(int io_num)

+{

+ GPIO.out_w1ts |= (0x1 << io_num);

+}

+//FIXME: esp32

+__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_LOW(int io_num)

+{

+ GPIO.out_w1tc |= (0x1 << io_num);

+}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_HIGH(int io_num)

+{

+ gpio_ll_set_level(&GPIO, io_num, 1);

+}

+__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_LOW(int io_num)

+{

+ gpio_ll_set_level(&GPIO, io_num, 0);

+}

+#endif

+

+

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

+__STATIC_INLINE __UNUSED int GPIO_GET_LEVEL(int io_num)

+{

+ return ((GPIO.in >> io_num) & 0x1) ? 1 : 0;

+}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__STATIC_INLINE __UNUSED int GPIO_GET_LEVEL(int io_num)

+{

+ return gpio_ll_get_level(&GPIO, io_num);

+}

#endif

-__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_HIGH(int io_num)

-{

- GPIO.out_w1ts |= (0x1 << io_num);

-}

-

-

-#ifdef CONFIG_IDF_TARGET_ESP32

+#if defined CONFIG_IDF_TARGET_ESP32 || defined CONFIG_IDF_TARGET_ESP32C3

__STATIC_INLINE __UNUSED void GPIO_PULL_UP_ONLY_SET(int io_num)

{

// disable pull down

@@ -82,12 +128,6 @@ __STATIC_INLINE __UNUSED void GPIO_PULL_UP_ONLY_SET(int io_num)

#endif

-//FIXME: esp32

-__STATIC_INLINE __UNUSED void GPIO_SET_LEVEL_LOW(int io_num)

-{

- GPIO.out_w1tc |= (0x1 << io_num);

-}

-

// static void GPIO_SET_DIRECTION_NORMAL_IN(int io_num)

// {

// GPIO.enable_w1tc |= (0x1 << io_num);

diff --git a/components/DAP/source/SW_DP.c b/components/DAP/source/SW_DP.c

index b47017e..8fcb8e3 100644

--- a/components/DAP/source/SW_DP.c

+++ b/components/DAP/source/SW_DP.c

@@ -238,7 +238,7 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

requestByte = constantBits | (((uint8_t)(request & 0xFU)) << 1U) | (ParityEvenUint8(request & 0xFU) << 5U);

/* For 4bit, Parity can be equivalent to 8bit with all 0 high bits */

- #if (PRINT_SWD_PROTOCOL == 1)

+#if (PRINT_SWD_PROTOCOL == 1)

switch (requestByte)

{

case 0xA5U:

@@ -282,7 +282,7 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

os_printf("Unknown:%08x\r\n", requestByte);

break;

}

- #endif

+#endif

if (request & DAP_TRANSFER_RnW) {

/* Read data */

@@ -304,11 +304,15 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

}

else if ((ack == DAP_TRANSFER_WAIT) || (ack == DAP_TRANSFER_FAULT)) {

- ////FIXME: esp32 // DAP_SPI_Fast_Cycle();

- DAP_SPI_Generate_Cycle(1);

- #if (PRINT_SWD_PROTOCOL == 1)

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

+ DAP_SPI_Generate_Cycle(1);

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ DAP_SPI_Fast_Cycle();

+#endif

+

+#if (PRINT_SWD_PROTOCOL == 1)

os_printf("WAIT\r\n");

- #endif

+#endif

// return DAP_TRANSFER_WAIT;

}

@@ -322,9 +326,9 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

DAP_SPI_Disable();

PIN_SWDIO_TMS_SET();

- #if (PRINT_SWD_PROTOCOL == 1)

+#if (PRINT_SWD_PROTOCOL == 1)

os_printf("Protocol Error: Read\r\n");

- #endif

+#endif

}

return ((uint8_t)ack);

@@ -352,9 +356,9 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

/* already turnaround. */

/* TODO: overrun transfer -> for read */

- #if (PRINT_SWD_PROTOCOL == 1)

+#if (PRINT_SWD_PROTOCOL == 1)

os_printf("WAIT\r\n");

- #endif

+#endif

}

else {

@@ -368,9 +372,9 @@ static uint8_t SWD_Transfer_SPI (uint32_t request, uint32_t *data) {

DAP_SPI_Disable();

PIN_SWDIO_TMS_SET();

- #if (PRINT_SWD_PROTOCOL == 1)

+#if (PRINT_SWD_PROTOCOL == 1)

os_printf("Protocol Error: Write\r\n");

- #endif

+#endif

}

return ((uint8_t)ack);

diff --git a/components/DAP/source/spi_op.c b/components/DAP/source/spi_op.c

index 8a0ada9..473a285 100644

--- a/components/DAP/source/spi_op.c

+++ b/components/DAP/source/spi_op.c

@@ -5,10 +5,11 @@

* @change: 2020-11-25 first version

* 2021-2-11 Support SWD sequence

* 2021-3-10 Support 3-wire SPI

- * @version 0.3

- * @date 2021-3-10

+ * 2022-9-15 Support ESP32C3

+ * @version 0.4

+ * @date 2022-9-15

*

- * @copyright Copyright (c) 2021

+ * @copyright MIT License

*

*/

#include "sdkconfig.h"

@@ -27,6 +28,8 @@

#define DAP_SPI SPI1

#elif defined CONFIG_IDF_TARGET_ESP32

#define DAP_SPI SPI2

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define DAP_SPI GPSPI2

#else

#error unknown hardware

#endif

@@ -35,9 +38,31 @@

#ifdef CONFIG_IDF_TARGET_ESP8266

#define SET_MOSI_BIT_LEN(x) DAP_SPI.user1.usr_mosi_bitlen = x

#define SET_MISO_BIT_LEN(x) DAP_SPI.user1.usr_miso_bitlen = x

+ #define START_AND_WAIT_SPI_TRANSMISSION_DONE() \

+ do { \

+ DAP_SPI.cmd.usr = 1; \

+ while (DAP_SPI.cmd.usr) continue; \

+ } while(0)

+

#elif defined CONFIG_IDF_TARGET_ESP32

#define SET_MOSI_BIT_LEN(x) DAP_SPI.mosi_dlen.usr_mosi_dbitlen = x

#define SET_MISO_BIT_LEN(x) DAP_SPI.miso_dlen.usr_miso_dbitlen = x

+ #define START_AND_WAIT_SPI_TRANSMISSION_DONE() \

+ do { \

+ DAP_SPI.cmd.usr = 1; \

+ while (DAP_SPI.cmd.usr) continue; \

+ } while(0)

+

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define SET_MOSI_BIT_LEN(x) DAP_SPI.ms_dlen.ms_data_bitlen = x

+ #define SET_MISO_BIT_LEN(x) DAP_SPI.ms_dlen.ms_data_bitlen = x

+ #define START_AND_WAIT_SPI_TRANSMISSION_DONE() \

+ do { \

+ DAP_SPI.cmd.update = 1; \

+ while (DAP_SPI.cmd.update) continue; \

+ DAP_SPI.cmd.usr = 1; \

+ while (DAP_SPI.cmd.usr) continue; \

+ } while(0)

#endif

/**

@@ -66,6 +91,7 @@ void DAP_SPI_WriteBits(const uint8_t count, const uint8_t *buf)

// have data to send

DAP_SPI.user.usr_mosi = 1;

+ DAP_SPI.user.usr_miso = 0;

SET_MOSI_BIT_LEN(count - 1);

// copy data to reg

switch (count)

@@ -102,10 +128,7 @@ void DAP_SPI_WriteBits(const uint8_t count, const uint8_t *buf)

}

}

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

}

@@ -131,10 +154,7 @@ void DAP_SPI_ReadBits(const uint8_t count, uint8_t *buf) {

SET_MISO_BIT_LEN(count - 1U);

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for reading to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

#if (USE_SPI_SIO == 1)

DAP_SPI.user.sio = false;

@@ -151,7 +171,7 @@ void DAP_SPI_ReadBits(const uint8_t count, uint8_t *buf) {

buf[i-1] = buf[i-1] & ((2 >> (count % 8)) - 1);

}

-

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

/**

* @brief Step1: Packet Request

*

@@ -179,10 +199,7 @@ __FORCEINLINE void DAP_SPI_Send_Header(const uint8_t packetHeaderData, uint8_t *

// copy data to reg

DAP_SPI.data_buf[0] = (packetHeaderData << 0) | (0U << 8) | (0U << 16) | (0U << 24);

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

#if (USE_SPI_SIO == 1)

DAP_SPI.user.sio = false;

@@ -190,7 +207,41 @@ __FORCEINLINE void DAP_SPI_Send_Header(const uint8_t packetHeaderData, uint8_t *

dataBuf = DAP_SPI.data_buf[0];

*ack = (dataBuf >> 1) & 0b111;

+} // defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__FORCEINLINE void DAP_SPI_Send_Header(const uint8_t packetHeaderData, uint8_t *ack, uint8_t TrnAfterACK)

+{

+ uint32_t dataBuf;

+

+ // have data to send

+ DAP_SPI.user.usr_mosi = 0;

+ DAP_SPI.user.usr_command = 1;

+ DAP_SPI.user.usr_miso = 1;

+

+ // 8bits Header + 1 bit Trn(Before ACK) - 1(prescribed)

+ DAP_SPI.user2.usr_command_bitlen = 8U + 1U - 1U;

+ DAP_SPI.user2.usr_command_value = packetHeaderData;

+

+

+#if (USE_SPI_SIO == 1)

+ DAP_SPI.user.sio = true;

+#endif

+

+ // 3bits ACK + TrnAferACK - 1(prescribed)

+ SET_MISO_BIT_LEN(3U + TrnAfterACK - 1U);

+

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

+

+#if (USE_SPI_SIO == 1)

+ DAP_SPI.user.sio = false;

+#endif

+

+ DAP_SPI.user.usr_command = 0;

+

+ dataBuf = DAP_SPI.data_buf[0];

+ *ack = dataBuf & 0b111;

}

+#endif

/**

@@ -211,13 +262,10 @@ __FORCEINLINE void DAP_SPI_Read_Data(uint32_t *resData, uint8_t *resParity)

DAP_SPI.user.sio = true;

#endif

- // 1 bit Trn(End) + 3bits ACK + 32bis data + 1bit parity - 1(prescribed)

+ // 1 bit Trn(End) + 32bis data + 1bit parity - 1(prescribed)

SET_MISO_BIT_LEN(1U + 32U + 1U - 1U);

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

#if (USE_SPI_SIO == 1)

DAP_SPI.user.sio = false;

@@ -227,9 +275,10 @@ __FORCEINLINE void DAP_SPI_Read_Data(uint32_t *resData, uint8_t *resParity)

pU32Data[1] = DAP_SPI.data_buf[1];

*resData = (dataBuf >> 0U) & 0xFFFFFFFFU; // 32bits Response Data

- *resParity = (dataBuf >> (0U + 32U)) & 1U; // 3bits ACK + 32bis data

+ *resParity = (dataBuf >> (0U + 32U)) & 1U; // 1bit parity

}

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

/**

* @brief Step2: Write Data

*

@@ -247,12 +296,26 @@ __FORCEINLINE void DAP_SPI_Write_Data(uint32_t data, uint8_t parity)

DAP_SPI.data_buf[0] = data;

DAP_SPI.data_buf[1] = parity;

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__FORCEINLINE void DAP_SPI_Write_Data(uint32_t data, uint8_t parity)

+{

+ DAP_SPI.user.usr_mosi = 1;

+ DAP_SPI.user.usr_miso = 0;

+ // esp32c3 can not send 33 bits of data correctly, we need to send an additional bit

+ // that will not be recognized as the start bit.

+ SET_MOSI_BIT_LEN(32U + 1U + 1U - 1U);

+ DAP_SPI.data_buf[0] = data;

+ DAP_SPI.data_buf[1] = parity == 0 ? 0b00 : 0b01;

+

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

+}

+#endif

+

+

+#if defined CONFIG_IDF_TARGET_ESP8266 || defined CONFIG_IDF_TARGET_ESP32

/**

* @brief Generate Clock Cycle

*

@@ -267,14 +330,23 @@ __FORCEINLINE void DAP_SPI_Generate_Cycle(uint8_t num)

DAP_SPI.data_buf[0] = 0x00000000U;

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

- // TODO: not wait?

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__FORCEINLINE void DAP_SPI_Generate_Cycle(uint8_t num)

+{

+ //// TODO: It may take long time to generate just one clock

+ DAP_SPI.user.usr_mosi = 0;

+ DAP_SPI.user.usr_miso = 1;

-#ifdef CONFIG_IDF_TARGET_ESP32

+ // esp32c3 can not send a single bit, therefore we use read operation instead.

+ SET_MISO_BIT_LEN(num - 1U);

+

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

+}

+#endif

+

+#if defined CONFIG_IDF_TARGET_ESP32 || defined CONFIG_IDF_TARGET_ESP32C3

/**

* @brief Quickly generate 1 clock

*

@@ -299,10 +371,7 @@ __FORCEINLINE void DAP_SPI_Protocol_Error_Read()

DAP_SPI.data_buf[0] = 0xFFFFFFFFU;

DAP_SPI.data_buf[1] = 0xFFFFFFFFU;

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

}

@@ -319,8 +388,5 @@ __FORCEINLINE void DAP_SPI_Protocol_Error_Write()

DAP_SPI.data_buf[0] = 0xFFFFFFFFU;

DAP_SPI.data_buf[1] = 0xFFFFFFFFU;

- // Start transmission

- DAP_SPI.cmd.usr = 1;

- // Wait for sending to complete

- while (DAP_SPI.cmd.usr) continue;

+ START_AND_WAIT_SPI_TRANSMISSION_DONE();

}

diff --git a/components/DAP/source/spi_switch.c b/components/DAP/source/spi_switch.c

index e334e11..50a635a 100644

--- a/components/DAP/source/spi_switch.c

+++ b/components/DAP/source/spi_switch.c

@@ -4,10 +4,11 @@

* @brief Switching between SPI mode and IO mode

* @change: 2020-11-25 first version

* 2021-2-11 Transmission mode switching test passed

- * @version 0.2

- * @date 2021-2-11

+ * 2022-9-15 Support ESP32C3

+ * @version 0.4

+ * @date 2021-9-15

*

- * @copyright Copyright (c) 2021

+ * @copyright MIT License

*

*/

#include "sdkconfig.h"

@@ -26,7 +27,8 @@

#define FUNC_SPI 1

#define SPI2_HOST 1

#define SPI_LL_RST_MASK (SPI_OUT_RST | SPI_IN_RST | SPI_AHBM_RST | SPI_AHBM_FIFO_RST)

-

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define DAP_SPI GPSPI2

#else

#error unknown hardware

#endif

@@ -93,7 +95,7 @@ void DAP_SPI_Init()

// Enable soft reset

DAP_SPI.slave.sync_reset = true;

- // Set the clock polarity and phase CPOL = CPHA = 0

+ // Set the clock polarity and phase CPOL = 1, CPHA = 0

DAP_SPI.pin.ck_idle_edge = 1; // HIGH while idle

DAP_SPI.user.ck_out_edge = 0;

@@ -245,7 +247,7 @@ void DAP_SPI_Init()

DAP_SPI.ctrl2.miso_delay_num = 0;

- // Set the clock polarity and phase CPOL = CPHA = 1

+ // Set the clock polarity and phase CPOL = 1, CPHA = 0

DAP_SPI.pin.ck_idle_edge = 1; // HIGH while idle

DAP_SPI.user.ck_out_edge = 0;

@@ -253,6 +255,102 @@ void DAP_SPI_Init()

DAP_SPI.user.usr_command = 0;

DAP_SPI.user.usr_addr = 0;

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+void DAP_SPI_Init()

+{

+ periph_ll_enable_clk_clear_rst(PERIPH_SPI2_MODULE);

+

+ // In esp32, the driving of GPIO should be stopped,

+ // otherwise there will be issue in the spi

+ GPIO.out_w1tc.out_w1tc = (0x1 << 6);

+ GPIO.out_w1tc.out_w1tc = (0x1 << 7);

+

+

+ // We will use IO_MUX to get the maximum speed.

+ GPIO.func_in_sel_cfg[FSPID_IN_IDX].sig_in_sel = 0; // IO_MUX direct connnect

+ PIN_INPUT_ENABLE(IO_MUX_GPIO7_REG); // MOSI

+ GPIO.func_out_sel_cfg[7].oen_sel = 0; // use output enable signal from peripheral

+ GPIO.func_out_sel_cfg[7].oen_inv_sel = 0; // do not invert the output value

+ PIN_FUNC_SELECT(IO_MUX_GPIO7_REG, FUNC_MTDO_FSPID);

+

+

+ GPIO.func_in_sel_cfg[FSPICLK_IN_IDX].sig_in_sel = 0;

+ PIN_INPUT_ENABLE(IO_MUX_GPIO6_REG); // SCLK

+ GPIO.func_out_sel_cfg[6].oen_sel = 0;

+ GPIO.func_out_sel_cfg[6].oen_inv_sel = 0;

+ PIN_FUNC_SELECT(IO_MUX_GPIO6_REG, FUNC_MTCK_FSPICLK);

+

+

+ // Not using DMA

+ // esp32c3 only

+ DAP_SPI.user.usr_conf_nxt = 0;

+ DAP_SPI.slave.usr_conf = 0;

+ DAP_SPI.dma_conf.dma_rx_ena = 0;

+ DAP_SPI.dma_conf.dma_tx_ena = 0;

+

+ // Set to Master mode

+ DAP_SPI.slave.slave_mode = false;

+

+ // use all 64 bytes of the buffer

+ DAP_SPI.user.usr_mosi_highpart = false;

+ DAP_SPI.user.usr_miso_highpart = false;

+

+ // Disable cs pin

+ DAP_SPI.user.cs_setup = false;

+ DAP_SPI.user.cs_hold = false;

+

+ // Disable CS signal

+ DAP_SPI.misc.cs0_dis = 1;

+ DAP_SPI.misc.cs1_dis = 1;

+ DAP_SPI.misc.cs2_dis = 1;

+ DAP_SPI.misc.cs3_dis = 1;

+ DAP_SPI.misc.cs4_dis = 1;

+ DAP_SPI.misc.cs5_dis = 1;

+

+ // Duplex transmit

+ DAP_SPI.user.doutdin = false; // half dulex

+

+ // Set data bit order

+ DAP_SPI.ctrl.wr_bit_order = 1; // SWD -> LSB

+ DAP_SPI.ctrl.rd_bit_order = 1; // SWD -> LSB

+

+ // Set dummy

+ DAP_SPI.user.usr_dummy = 0; // not use

+

+ // Set spi clk: 40Mhz 50% duty

+ // CLEAR_PERI_REG_MASK(PERIPHS_IO_MUX_CONF_U, SPI1_CLK_EQU_SYS_CLK);

+

+ // See esp32c3 TRM `SPI_CLOCK_REG`

+ DAP_SPI.clock.clk_equ_sysclk = false;

+ DAP_SPI.clock.clkdiv_pre = 0;

+ DAP_SPI.clock.clkcnt_n = SPI_40MHz_DIV - 1;

+ DAP_SPI.clock.clkcnt_h = SPI_40MHz_DIV / 2 - 1;

+ DAP_SPI.clock.clkcnt_l = SPI_40MHz_DIV - 1;

+

+ // MISO delay setting

+ DAP_SPI.user.rsck_i_edge = true;

+ DAP_SPI.din_mode.din0_mode = 0;

+ DAP_SPI.din_mode.din1_mode = 0;

+ DAP_SPI.din_mode.din2_mode = 0;

+ DAP_SPI.din_mode.din3_mode = 0;

+ DAP_SPI.din_num.din0_num = 0;

+ DAP_SPI.din_num.din1_num = 0;

+ DAP_SPI.din_num.din2_num = 0;

+ DAP_SPI.din_num.din3_num = 0;

+

+ // Set the clock polarity and phase CPOL = 1, CPHA = 0

+ DAP_SPI.misc.ck_idle_edge = 1; // HIGH while idle

+ DAP_SPI.user.ck_out_edge = 0;

+

+ // enable spi clock

+ DAP_SPI.clk_gate.clk_en = 1;

+ DAP_SPI.clk_gate.mst_clk_active = 1;

+ DAP_SPI.clk_gate.mst_clk_sel = 1;

+

+ // No command and addr for now

+ DAP_SPI.user.usr_command = 0;

+ DAP_SPI.user.usr_addr = 0;

+}

#endif

@@ -305,6 +403,19 @@ __FORCEINLINE void DAP_SPI_Deinit()

// disable MOSI pull up

// REG_CLR_BIT(GPIO_PIN_MUX_REG[13], FUN_PU);

}

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+__FORCEINLINE void DAP_SPI_Deinit()

+{

+ PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[6], PIN_FUNC_GPIO);

+ PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[7], PIN_FUNC_GPIO); // MOSI

+

+ // enable SWCLK output

+ GPIO.enable_w1ts.enable_w1ts = (0x01 << 6);

+

+ // enable MOSI output & input

+ GPIO.enable_w1ts.enable_w1ts |= (0x1 << 7);

+ PIN_INPUT_ENABLE(GPIO_PIN_MUX_REG[7]);

+}

#endif

@@ -328,7 +439,26 @@ __FORCEINLINE void DAP_SPI_Release()

PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[14], PIN_FUNC_GPIO);

GPIO.enable_w1ts = (0x01 << 14);

}

-#endif // CONFIG_IDF_TARGET_ESP32

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+/**

+ * @brief Gain control of SPI

+ *

+ */

+__FORCEINLINE void DAP_SPI_Acquire()

+{

+ PIN_FUNC_SELECT(IO_MUX_GPIO6_REG, FUNC_MTCK_FSPICLK);

+}

+

+

+/**

+ * @brief Release control of SPI

+ *

+ */

+__FORCEINLINE void DAP_SPI_Release()

+{

+ PIN_FUNC_SELECT(IO_MUX_GPIO6_REG, FUNC_MTCK_GPIO6);

+}

+#endif

/**

* @brief Use SPI acclerate

*

diff --git a/components/corsacOTA b/components/corsacOTA

index 98e9ffe..eecc603 160000

--- a/components/corsacOTA

+++ b/components/corsacOTA

@@ -1 +1 @@

-Subproject commit 98e9ffeb3b08e91743b147cf292dfd76259fc380

+Subproject commit eecc603dc5db13aecd4253804d57f9a0a285bffa

diff --git a/main/main.c b/main/main.c

index 1707226..63a1b6f 100644

--- a/main/main.c

+++ b/main/main.c

@@ -10,6 +10,7 @@

#include

#include

+#include "sdkconfig.h"

#include "main/tcp_server.h"

#include "main/tcp_netconn.h"

#include "main/kcp_server.h"

@@ -128,7 +129,14 @@ void app_main() {

// DAP handle task

xTaskCreate(DAP_Thread, "DAP_Task", 2048, NULL, 10, &kDAPTaskHandle);

+#if defined CONFIG_IDF_TARGET_ESP8266

+ #define UART_BRIDGE_TASK_STACK_SIZE 1024

+#else

+ #define UART_BRIDGE_TASK_STACK_SIZE 2048

+#endif

+

+ //// FIXME: potential stack overflow

#if (USE_UART_BRIDGE == 1)

- xTaskCreate(uart_bridge_task, "uart_server", 1024, NULL, 2, NULL);

+ xTaskCreate(uart_bridge_task, "uart_server", UART_BRIDGE_TASK_STACK_SIZE, NULL, 2, NULL);

#endif

}

diff --git a/main/timer.c b/main/timer.c

index 9099d9f..e2e4159 100644

--- a/main/timer.c

+++ b/main/timer.c

@@ -55,7 +55,7 @@ uint32_t get_timer_count()

#ifdef CONFIG_IDF_TARGET_ESP8266

return (uint32_t)frc2->count.data;

-#elif defined CONFIG_IDF_TARGET_ESP32

+#elif defined CONFIG_IDF_TARGET_ESP32 || defined CONFIG_IDF_TARGET_ESP32C3

return 0;

#else

#error unknown hardware

diff --git a/main/uart_bridge.c b/main/uart_bridge.c

index 2c8a3cb..453f33d 100644

--- a/main/uart_bridge.c

+++ b/main/uart_bridge.c

@@ -59,6 +59,13 @@ THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND

#elif defined CONFIG_IDF_TARGET_ESP32

#define UART_BRIDGE_TX UART_NUM_2

#define UART_BRIDGE_RX UART_NUM_2

+ #define UART_BRIDGE_TX_PIN 23

+ #define UART_BRIDGE_RX_PIN 22

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define UART_BRIDGE_TX UART_NUM_1

+ #define UART_BRIDGE_RX UART_NUM_1

+ #define UART_BRIDGE_TX_PIN 19

+ #define UART_BRIDGE_RX_PIN 18 // PIN18 has 50000ns glitch during the power-up

#else

#error unknown hardware

#endif

@@ -192,6 +199,10 @@ static void uart_bridge_setup() {

uart_driver_install(UART_BRIDGE_TX, 0, UART_BUF_SIZE, 0, NULL, 0); // TX only

}

+#if defined CONFIG_IDF_TARGET_ESP32 || defined CONFIG_IDF_TARGET_ESP32C3

+ uart_set_pin(UART_BRIDGE_TX, UART_BRIDGE_TX_PIN, UART_BRIDGE_RX_PIN, -1, -1);

+#endif

+

}

void uart_bridge_init() {

diff --git a/main/wifi_configuration.h b/main/wifi_configuration.h

index 7684c1b..47ef499 100644

--- a/main/wifi_configuration.h

+++ b/main/wifi_configuration.h

@@ -36,16 +36,16 @@ static struct {

#define DAP_IP_NETMASK 255, 255, 255, 0

//

-#define USE_OTA 1

+#define USE_OTA 0

-#define USE_UART_BRIDGE 1

+#define USE_UART_BRIDGE 0

#define UART_BRIDGE_PORT 1234

#define UART_BRIDGE_BAUDRATE 74880

//

+// DO NOT CHANGE

#define USE_TCP_NETCONN 0

-// DO NOT CHANGE

#define PORT 3240

#define CONFIG_EXAMPLE_IPV4 1

#define USE_KCP 0

diff --git a/main/wifi_handle.c b/main/wifi_handle.c

index c3ec842..9559002 100644

--- a/main/wifi_handle.c

+++ b/main/wifi_handle.c

@@ -21,6 +21,8 @@

#define PIN_LED_WIFI_STATUS 15

#elif defined CONFIG_IDF_TARGET_ESP32

#define PIN_LED_WIFI_STATUS 27

+#elif defined CONFIG_IDF_TARGET_ESP32C3

+ #define PIN_LED_WIFI_STATUS 10

#else

#error unknown hardware

#endif

diff --git a/sdkconfig.defaults.esp32c3 b/sdkconfig.defaults.esp32c3

new file mode 100644

index 0000000..57f349d

--- /dev/null

+++ b/sdkconfig.defaults.esp32c3

@@ -0,0 +1,1179 @@

+CONFIG_IDF_CMAKE=y

+CONFIG_IDF_TARGET_ARCH_RISCV=y

+CONFIG_IDF_TARGET="esp32c3"

+CONFIG_IDF_TARGET_ESP32C3=y

+CONFIG_IDF_FIRMWARE_CHIP_ID=0x0005

+

+#

+# SDK tool configuration

+#

+CONFIG_SDK_TOOLPREFIX="riscv32-esp-elf-"

+# CONFIG_SDK_TOOLCHAIN_SUPPORTS_TIME_WIDE_64_BITS is not set

+# end of SDK tool configuration

+

+#

+# Build type

+#

+CONFIG_APP_BUILD_TYPE_APP_2NDBOOT=y

+# CONFIG_APP_BUILD_TYPE_ELF_RAM is not set

+CONFIG_APP_BUILD_GENERATE_BINARIES=y

+CONFIG_APP_BUILD_BOOTLOADER=y

+CONFIG_APP_BUILD_USE_FLASH_SECTIONS=y

+# end of Build type

+

+#

+# Application manager

+#

+CONFIG_APP_COMPILE_TIME_DATE=y

+# CONFIG_APP_EXCLUDE_PROJECT_VER_VAR is not set

+# CONFIG_APP_EXCLUDE_PROJECT_NAME_VAR is not set

+# CONFIG_APP_PROJECT_VER_FROM_CONFIG is not set

+CONFIG_APP_RETRIEVE_LEN_ELF_SHA=16

+# end of Application manager

+

+#

+# Bootloader config

+#

+CONFIG_BOOTLOADER_OFFSET_IN_FLASH=0x0

+CONFIG_BOOTLOADER_COMPILER_OPTIMIZATION_SIZE=y

+# CONFIG_BOOTLOADER_COMPILER_OPTIMIZATION_DEBUG is not set

+# CONFIG_BOOTLOADER_COMPILER_OPTIMIZATION_PERF is not set

+# CONFIG_BOOTLOADER_COMPILER_OPTIMIZATION_NONE is not set

+# CONFIG_BOOTLOADER_LOG_LEVEL_NONE is not set

+# CONFIG_BOOTLOADER_LOG_LEVEL_ERROR is not set

+# CONFIG_BOOTLOADER_LOG_LEVEL_WARN is not set

+CONFIG_BOOTLOADER_LOG_LEVEL_INFO=y

+# CONFIG_BOOTLOADER_LOG_LEVEL_DEBUG is not set

+# CONFIG_BOOTLOADER_LOG_LEVEL_VERBOSE is not set

+CONFIG_BOOTLOADER_LOG_LEVEL=3

+CONFIG_BOOTLOADER_VDDSDIO_BOOST_1_9V=y

+# CONFIG_BOOTLOADER_FACTORY_RESET is not set

+# CONFIG_BOOTLOADER_APP_TEST is not set

+CONFIG_BOOTLOADER_REGION_PROTECTION_ENABLE=y

+CONFIG_BOOTLOADER_WDT_ENABLE=y

+# CONFIG_BOOTLOADER_WDT_DISABLE_IN_USER_CODE is not set

+CONFIG_BOOTLOADER_WDT_TIME_MS=9000

+# CONFIG_BOOTLOADER_APP_ROLLBACK_ENABLE is not set

+# CONFIG_BOOTLOADER_SKIP_VALIDATE_IN_DEEP_SLEEP is not set

+# CONFIG_BOOTLOADER_SKIP_VALIDATE_ON_POWER_ON is not set

+# CONFIG_BOOTLOADER_SKIP_VALIDATE_ALWAYS is not set

+CONFIG_BOOTLOADER_RESERVE_RTC_SIZE=0

+# CONFIG_BOOTLOADER_CUSTOM_RESERVE_RTC is not set

+CONFIG_BOOTLOADER_FLASH_XMC_SUPPORT=y

+# end of Bootloader config

+

+#

+# Security features

+#

+CONFIG_SECURE_BOOT_SUPPORTS_RSA=y

+CONFIG_SECURE_TARGET_HAS_SECURE_ROM_DL_MODE=y

+# CONFIG_SECURE_SIGNED_APPS_NO_SECURE_BOOT is not set

+# CONFIG_SECURE_BOOT is not set

+# CONFIG_SECURE_FLASH_ENC_ENABLED is not set

+# end of Security features

+

+#

+# Boot ROM Behavior

+#

+CONFIG_BOOT_ROM_LOG_ALWAYS_ON=y

+# CONFIG_BOOT_ROM_LOG_ALWAYS_OFF is not set

+# CONFIG_BOOT_ROM_LOG_ON_GPIO_HIGH is not set

+# CONFIG_BOOT_ROM_LOG_ON_GPIO_LOW is not set

+# end of Boot ROM Behavior

+

+#

+# Serial flasher config

+#

+CONFIG_ESPTOOLPY_BAUD_OTHER_VAL=115200

+# CONFIG_ESPTOOLPY_NO_STUB is not set

+# CONFIG_ESPTOOLPY_FLASHMODE_QIO is not set

+# CONFIG_ESPTOOLPY_FLASHMODE_QOUT is not set

+CONFIG_ESPTOOLPY_FLASHMODE_DIO=y

+# CONFIG_ESPTOOLPY_FLASHMODE_DOUT is not set

+CONFIG_ESPTOOLPY_FLASH_SAMPLE_MODE_STR=y

+CONFIG_ESPTOOLPY_FLASHMODE="dio"

+CONFIG_ESPTOOLPY_FLASHFREQ_80M=y

+# CONFIG_ESPTOOLPY_FLASHFREQ_40M is not set

+# CONFIG_ESPTOOLPY_FLASHFREQ_26M is not set

+# CONFIG_ESPTOOLPY_FLASHFREQ_20M is not set

+CONFIG_ESPTOOLPY_FLASHFREQ="80m"

+# CONFIG_ESPTOOLPY_FLASHSIZE_1MB is not set

+CONFIG_ESPTOOLPY_FLASHSIZE_2MB=y

+# CONFIG_ESPTOOLPY_FLASHSIZE_4MB is not set

+# CONFIG_ESPTOOLPY_FLASHSIZE_8MB is not set

+# CONFIG_ESPTOOLPY_FLASHSIZE_16MB is not set

+# CONFIG_ESPTOOLPY_FLASHSIZE_32MB is not set

+# CONFIG_ESPTOOLPY_FLASHSIZE_64MB is not set

+# CONFIG_ESPTOOLPY_FLASHSIZE_128MB is not set

+CONFIG_ESPTOOLPY_FLASHSIZE="2MB"

+CONFIG_ESPTOOLPY_FLASHSIZE_DETECT=y

+CONFIG_ESPTOOLPY_BEFORE_RESET=y

+# CONFIG_ESPTOOLPY_BEFORE_NORESET is not set

+CONFIG_ESPTOOLPY_BEFORE="default_reset"

+CONFIG_ESPTOOLPY_AFTER_RESET=y

+# CONFIG_ESPTOOLPY_AFTER_NORESET is not set

+CONFIG_ESPTOOLPY_AFTER="hard_reset"

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_CONSOLE is not set

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_9600B is not set

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_57600B is not set

+CONFIG_ESPTOOLPY_MONITOR_BAUD_115200B=y

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_230400B is not set

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_921600B is not set

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_2MB is not set

+# CONFIG_ESPTOOLPY_MONITOR_BAUD_OTHER is not set

+CONFIG_ESPTOOLPY_MONITOR_BAUD_OTHER_VAL=115200

+CONFIG_ESPTOOLPY_MONITOR_BAUD=115200

+# end of Serial flasher config

+

+#

+# Partition Table

+#

+CONFIG_PARTITION_TABLE_SINGLE_APP=y

+# CONFIG_PARTITION_TABLE_SINGLE_APP_LARGE is not set

+# CONFIG_PARTITION_TABLE_TWO_OTA is not set

+# CONFIG_PARTITION_TABLE_CUSTOM is not set

+CONFIG_PARTITION_TABLE_CUSTOM_FILENAME="partitions.csv"

+CONFIG_PARTITION_TABLE_FILENAME="partitions_singleapp.csv"

+CONFIG_PARTITION_TABLE_OFFSET=0x8000

+CONFIG_PARTITION_TABLE_MD5=y

+# end of Partition Table

+

+#

+# Compiler options

+#

+# CONFIG_COMPILER_OPTIMIZATION_DEFAULT is not set

+# CONFIG_COMPILER_OPTIMIZATION_SIZE is not set

+CONFIG_COMPILER_OPTIMIZATION_PERF=y

+# CONFIG_COMPILER_OPTIMIZATION_NONE is not set

+CONFIG_COMPILER_OPTIMIZATION_ASSERTIONS_ENABLE=y

+# CONFIG_COMPILER_OPTIMIZATION_ASSERTIONS_SILENT is not set

+# CONFIG_COMPILER_OPTIMIZATION_ASSERTIONS_DISABLE is not set

+CONFIG_COMPILER_OPTIMIZATION_ASSERTION_LEVEL=2

+# CONFIG_COMPILER_OPTIMIZATION_CHECKS_SILENT is not set

+CONFIG_COMPILER_HIDE_PATHS_MACROS=y

+# CONFIG_COMPILER_CXX_EXCEPTIONS is not set

+# CONFIG_COMPILER_CXX_RTTI is not set

+CONFIG_COMPILER_STACK_CHECK_MODE_NONE=y

+# CONFIG_COMPILER_STACK_CHECK_MODE_NORM is not set

+# CONFIG_COMPILER_STACK_CHECK_MODE_STRONG is not set

+# CONFIG_COMPILER_STACK_CHECK_MODE_ALL is not set

+# CONFIG_COMPILER_WARN_WRITE_STRINGS is not set

+# CONFIG_COMPILER_SAVE_RESTORE_LIBCALLS is not set

+# CONFIG_COMPILER_DISABLE_GCC8_WARNINGS is not set

+# CONFIG_COMPILER_DUMP_RTL_FILES is not set

+# end of Compiler options

+

+#

+# Component config

+#

+

+#

+# Application Level Tracing

+#

+# CONFIG_APPTRACE_DEST_JTAG is not set

+CONFIG_APPTRACE_DEST_NONE=y

+CONFIG_APPTRACE_LOCK_ENABLE=y

+# end of Application Level Tracing

+

+#

+# ESP-ASIO

+#

+# CONFIG_ASIO_SSL_SUPPORT is not set

+# end of ESP-ASIO

+

+#

+# Bluetooth

+#

+# CONFIG_BT_ENABLED is not set

+# end of Bluetooth

+

+#

+# CoAP Configuration

+#

+CONFIG_COAP_MBEDTLS_PSK=y

+# CONFIG_COAP_MBEDTLS_PKI is not set

+# CONFIG_COAP_MBEDTLS_DEBUG is not set

+CONFIG_COAP_LOG_DEFAULT_LEVEL=0

+# end of CoAP Configuration

+

+#

+# Driver configurations

+#

+

+#

+# ADC configuration

+#

+# CONFIG_ADC_FORCE_XPD_FSM is not set

+CONFIG_ADC_DISABLE_DAC=y

+# end of ADC configuration

+

+#

+# MCPWM configuration

+#

+# CONFIG_MCPWM_ISR_IN_IRAM is not set

+# end of MCPWM configuration

+

+#

+# SPI configuration

+#

+# CONFIG_SPI_MASTER_IN_IRAM is not set

+CONFIG_SPI_MASTER_ISR_IN_IRAM=y

+# CONFIG_SPI_SLAVE_IN_IRAM is not set

+CONFIG_SPI_SLAVE_ISR_IN_IRAM=y

+# end of SPI configuration

+

+#

+# TWAI configuration

+#

+# CONFIG_TWAI_ISR_IN_IRAM is not set

+# end of TWAI configuration

+

+#

+# UART configuration

+#

+CONFIG_UART_ISR_IN_IRAM=y

+# end of UART configuration

+

+#

+# GDMA Configuration

+#

+CONFIG_GDMA_CTRL_FUNC_IN_IRAM=y

+# CONFIG_GDMA_ISR_IRAM_SAFE is not set

+# end of GDMA Configuration

+# end of Driver configurations

+

+#

+# eFuse Bit Manager

+#

+# CONFIG_EFUSE_CUSTOM_TABLE is not set

+# CONFIG_EFUSE_VIRTUAL is not set

+CONFIG_EFUSE_MAX_BLK_LEN=256

+# end of eFuse Bit Manager

+

+#

+# ESP-TLS

+#

+CONFIG_ESP_TLS_USING_MBEDTLS=y

+CONFIG_ESP_TLS_USE_DS_PERIPHERAL=y

+# CONFIG_ESP_TLS_CLIENT_SESSION_TICKETS is not set

+# CONFIG_ESP_TLS_SERVER is not set

+# CONFIG_ESP_TLS_PSK_VERIFICATION is not set

+# CONFIG_ESP_TLS_INSECURE is not set

+# end of ESP-TLS

+

+#

+# ESP32C3-Specific

+#

+# CONFIG_ESP32C3_DEFAULT_CPU_FREQ_80 is not set

+CONFIG_ESP32C3_DEFAULT_CPU_FREQ_160=y

+CONFIG_ESP32C3_DEFAULT_CPU_FREQ_MHZ=160

+# CONFIG_ESP32C3_REV_MIN_0 is not set

+# CONFIG_ESP32C3_REV_MIN_1 is not set

+# CONFIG_ESP32C3_REV_MIN_2 is not set

+CONFIG_ESP32C3_REV_MIN_3=y

+# CONFIG_ESP32C3_REV_MIN_4 is not set

+CONFIG_ESP32C3_REV_MIN=3

+# CONFIG_ESP32C3_DEBUG_OCDAWARE is not set

+CONFIG_ESP32C3_BROWNOUT_DET=y

+CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_7=y

+# CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_6 is not set

+# CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_5 is not set

+# CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_4 is not set

+# CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_3 is not set

+# CONFIG_ESP32C3_BROWNOUT_DET_LVL_SEL_2 is not set

+CONFIG_ESP32C3_BROWNOUT_DET_LVL=7

+CONFIG_ESP32C3_TIME_SYSCALL_USE_RTC_SYSTIMER=y

+# CONFIG_ESP32C3_TIME_SYSCALL_USE_RTC is not set

+# CONFIG_ESP32C3_TIME_SYSCALL_USE_SYSTIMER is not set

+# CONFIG_ESP32C3_TIME_SYSCALL_USE_NONE is not set

+CONFIG_ESP32C3_RTC_CLK_SRC_INT_RC=y

+# CONFIG_ESP32C3_RTC_CLK_SRC_EXT_CRYS is not set

+# CONFIG_ESP32C3_RTC_CLK_SRC_EXT_OSC is not set

+# CONFIG_ESP32C3_RTC_CLK_SRC_INT_8MD256 is not set

+CONFIG_ESP32C3_RTC_CLK_CAL_CYCLES=1024

+# CONFIG_ESP32C3_NO_BLOBS is not set

+# end of ESP32C3-Specific

+

+#

+# ADC-Calibration

+#

+# end of ADC-Calibration

+

+#

+# Common ESP-related

+#

+CONFIG_ESP_ERR_TO_NAME_LOOKUP=y

+# end of Common ESP-related

+

+#

+# Ethernet

+#

+CONFIG_ETH_ENABLED=y

+CONFIG_ETH_USE_SPI_ETHERNET=y

+# CONFIG_ETH_SPI_ETHERNET_DM9051 is not set

+# CONFIG_ETH_SPI_ETHERNET_W5500 is not set

+# CONFIG_ETH_SPI_ETHERNET_KSZ8851SNL is not set

+# CONFIG_ETH_USE_OPENETH is not set

+# end of Ethernet

+

+#

+# Event Loop Library

+#

+# CONFIG_ESP_EVENT_LOOP_PROFILING is not set

+CONFIG_ESP_EVENT_POST_FROM_ISR=y

+CONFIG_ESP_EVENT_POST_FROM_IRAM_ISR=y

+# end of Event Loop Library

+

+#

+# GDB Stub

+#

+# end of GDB Stub

+

+#

+# ESP HTTP client

+#

+# CONFIG_ESP_HTTP_CLIENT_ENABLE_HTTPS is not set

+# CONFIG_ESP_HTTP_CLIENT_ENABLE_BASIC_AUTH is not set

+CONFIG_ESP_HTTP_CLIENT_ENABLE_DIGEST_AUTH=y

+# end of ESP HTTP client

+

+#

+# HTTP Server

+#

+CONFIG_HTTPD_MAX_REQ_HDR_LEN=512

+CONFIG_HTTPD_MAX_URI_LEN=512

+CONFIG_HTTPD_ERR_RESP_NO_DELAY=y

+CONFIG_HTTPD_PURGE_BUF_LEN=32

+# CONFIG_HTTPD_LOG_PURGE_DATA is not set

+# CONFIG_HTTPD_WS_SUPPORT is not set

+# end of HTTP Server

+

+#

+# ESP HTTPS OTA

+#

+# CONFIG_OTA_ALLOW_HTTP is not set

+# end of ESP HTTPS OTA

+

+#

+# ESP HTTPS server

+#

+# CONFIG_ESP_HTTPS_SERVER_ENABLE is not set

+# end of ESP HTTPS server

+

+#

+# Hardware Settings

+#

+

+#

+# MAC Config

+#

+CONFIG_ESP_MAC_ADDR_UNIVERSE_WIFI_STA=y

+CONFIG_ESP_MAC_ADDR_UNIVERSE_WIFI_AP=y

+CONFIG_ESP_MAC_ADDR_UNIVERSE_BT=y

+CONFIG_ESP_MAC_ADDR_UNIVERSE_ETH=y

+# CONFIG_ESP32C3_UNIVERSAL_MAC_ADDRESSES_TWO is not set

+CONFIG_ESP32C3_UNIVERSAL_MAC_ADDRESSES_FOUR=y

+CONFIG_ESP32C3_UNIVERSAL_MAC_ADDRESSES=4

+# end of MAC Config

+

+#

+# Sleep Config

+#

+CONFIG_ESP_SLEEP_POWER_DOWN_FLASH=y

+CONFIG_ESP_SLEEP_GPIO_RESET_WORKAROUND=y

+# CONFIG_ESP_SLEEP_FLASH_LEAKAGE_WORKAROUND is not set

+# end of Sleep Config

+

+#

+# RTC Clock Config

+#

+CONFIG_RTC_CLOCK_BBPLL_POWER_ON_WITH_USB=y

+# end of RTC Clock Config

+# end of Hardware Settings

+

+#

+# IPC (Inter-Processor Call)

+#

+CONFIG_ESP_IPC_TASK_STACK_SIZE=1536

+# end of IPC (Inter-Processor Call)

+

+#

+# LCD and Touch Panel

+#

+

+#

+# LCD Peripheral Configuration

+#

+CONFIG_LCD_PANEL_IO_FORMAT_BUF_SIZE=32

+# end of LCD Peripheral Configuration

+# end of LCD and Touch Panel

+

+#

+# ESP NETIF Adapter

+#

+CONFIG_ESP_NETIF_IP_LOST_TIMER_INTERVAL=120

+CONFIG_ESP_NETIF_TCPIP_LWIP=y

+# CONFIG_ESP_NETIF_LOOPBACK is not set

+CONFIG_ESP_NETIF_TCPIP_ADAPTER_COMPATIBLE_LAYER=y

+# end of ESP NETIF Adapter

+

+#

+# PHY

+#

+CONFIG_ESP_PHY_CALIBRATION_AND_DATA_STORAGE=y

+# CONFIG_ESP_PHY_INIT_DATA_IN_PARTITION is not set

+CONFIG_ESP_PHY_MAX_WIFI_TX_POWER=20

+CONFIG_ESP_PHY_MAX_TX_POWER=20

+CONFIG_ESP_PHY_ENABLE_USB=y

+# end of PHY

+

+#

+# Power Management

+#

+# CONFIG_PM_ENABLE is not set

+CONFIG_PM_SLP_DEFAULT_PARAMS_OPT=y

+CONFIG_PM_POWER_DOWN_CPU_IN_LIGHT_SLEEP=y

+# end of Power Management

+

+#

+# ESP System Settings

+#

+# CONFIG_ESP_SYSTEM_PANIC_PRINT_HALT is not set

+CONFIG_ESP_SYSTEM_PANIC_PRINT_REBOOT=y

+# CONFIG_ESP_SYSTEM_PANIC_SILENT_REBOOT is not set

+# CONFIG_ESP_SYSTEM_PANIC_GDBSTUB is not set

+# CONFIG_ESP_SYSTEM_GDBSTUB_RUNTIME is not set

+CONFIG_ESP_SYSTEM_SINGLE_CORE_MODE=y

+CONFIG_ESP_SYSTEM_RTC_FAST_MEM_AS_HEAP_DEPCHECK=y

+CONFIG_ESP_SYSTEM_ALLOW_RTC_FAST_MEM_AS_HEAP=y

+# CONFIG_ESP_SYSTEM_USE_EH_FRAME is not set

+

+#

+# Memory protection

+#

+CONFIG_ESP_SYSTEM_MEMPROT_DEPCHECK=y

+CONFIG_ESP_SYSTEM_MEMPROT_FEATURE=y

+CONFIG_ESP_SYSTEM_MEMPROT_FEATURE_LOCK=y

+CONFIG_ESP_SYSTEM_MEMPROT_CPU_PREFETCH_PAD_SIZE=16

+CONFIG_ESP_SYSTEM_MEMPROT_MEM_ALIGN_SIZE=512

+# end of Memory protection

+

+CONFIG_ESP_SYSTEM_EVENT_QUEUE_SIZE=32

+CONFIG_ESP_SYSTEM_EVENT_TASK_STACK_SIZE=2304

+CONFIG_ESP_MAIN_TASK_STACK_SIZE=3584

+CONFIG_ESP_MAIN_TASK_AFFINITY_CPU0=y

+# CONFIG_ESP_MAIN_TASK_AFFINITY_NO_AFFINITY is not set

+CONFIG_ESP_MAIN_TASK_AFFINITY=0x0

+CONFIG_ESP_MINIMAL_SHARED_STACK_SIZE=2048

+CONFIG_ESP_CONSOLE_UART_DEFAULT=y

+# CONFIG_ESP_CONSOLE_USB_SERIAL_JTAG is not set

+# CONFIG_ESP_CONSOLE_UART_CUSTOM is not set

+# CONFIG_ESP_CONSOLE_NONE is not set

+# CONFIG_ESP_CONSOLE_SECONDARY_NONE is not set

+CONFIG_ESP_CONSOLE_SECONDARY_USB_SERIAL_JTAG=y

+CONFIG_ESP_CONSOLE_UART=y

+CONFIG_ESP_CONSOLE_UART_NUM=0

+CONFIG_ESP_CONSOLE_UART_BAUDRATE=115200

+# CONFIG_ESP_INT_WDT is not set

+# CONFIG_ESP_TASK_WDT is not set

+# CONFIG_ESP_PANIC_HANDLER_IRAM is not set

+# CONFIG_ESP_DEBUG_STUBS_ENABLE is not set

+CONFIG_ESP_SYSTEM_CHECK_INT_LEVEL_4=y

+# end of ESP System Settings

+

+#

+# High resolution timer (esp_timer)

+#

+# CONFIG_ESP_TIMER_PROFILING is not set

+CONFIG_ESP_TIME_FUNCS_USE_RTC_TIMER=y

+CONFIG_ESP_TIME_FUNCS_USE_ESP_TIMER=y

+CONFIG_ESP_TIMER_TASK_STACK_SIZE=3584

+CONFIG_ESP_TIMER_INTERRUPT_LEVEL=1

+# CONFIG_ESP_TIMER_SUPPORTS_ISR_DISPATCH_METHOD is not set

+CONFIG_ESP_TIMER_IMPL_SYSTIMER=y

+# end of High resolution timer (esp_timer)

+

+#

+# Wi-Fi

+#

+CONFIG_ESP32_WIFI_ENABLED=y

+CONFIG_ESP32_WIFI_STATIC_RX_BUFFER_NUM=10

+CONFIG_ESP32_WIFI_DYNAMIC_RX_BUFFER_NUM=32

+# CONFIG_ESP32_WIFI_STATIC_TX_BUFFER is not set

+CONFIG_ESP32_WIFI_DYNAMIC_TX_BUFFER=y

+CONFIG_ESP32_WIFI_TX_BUFFER_TYPE=1

+CONFIG_ESP32_WIFI_DYNAMIC_TX_BUFFER_NUM=32

+# CONFIG_ESP32_WIFI_CSI_ENABLED is not set

+CONFIG_ESP32_WIFI_AMPDU_TX_ENABLED=y

+CONFIG_ESP32_WIFI_TX_BA_WIN=6

+CONFIG_ESP32_WIFI_AMPDU_RX_ENABLED=y

+CONFIG_ESP32_WIFI_RX_BA_WIN=6

+CONFIG_ESP32_WIFI_NVS_ENABLED=y

+CONFIG_ESP32_WIFI_SOFTAP_BEACON_MAX_LEN=752

+CONFIG_ESP32_WIFI_MGMT_SBUF_NUM=32

+CONFIG_ESP32_WIFI_IRAM_OPT=y

+CONFIG_ESP32_WIFI_RX_IRAM_OPT=y

+CONFIG_ESP32_WIFI_ENABLE_WPA3_SAE=y

+CONFIG_ESP_WIFI_SLP_IRAM_OPT=y

+CONFIG_ESP_WIFI_SLP_DEFAULT_MIN_ACTIVE_TIME=50

+CONFIG_ESP_WIFI_SLP_DEFAULT_MAX_ACTIVE_TIME=10

+# CONFIG_ESP_WIFI_FTM_ENABLE is not set

+# CONFIG_ESP_WIFI_STA_DISCONNECTED_PM_ENABLE is not set

+# CONFIG_ESP_WIFI_EXTERNAL_COEXIST_ENABLE is not set

+# CONFIG_ESP_WIFI_GCMP_SUPPORT is not set

+# CONFIG_ESP_WIFI_GMAC_SUPPORT is not set

+CONFIG_ESP_WIFI_SOFTAP_SUPPORT=y

+# end of Wi-Fi

+

+#

+# Core dump

+#

+# CONFIG_ESP_COREDUMP_ENABLE_TO_FLASH is not set

+# CONFIG_ESP_COREDUMP_ENABLE_TO_UART is not set

+CONFIG_ESP_COREDUMP_ENABLE_TO_NONE=y

+# end of Core dump

+

+#

+# FAT Filesystem support

+#

+# CONFIG_FATFS_CODEPAGE_DYNAMIC is not set

+CONFIG_FATFS_CODEPAGE_437=y

+# CONFIG_FATFS_CODEPAGE_720 is not set

+# CONFIG_FATFS_CODEPAGE_737 is not set

+# CONFIG_FATFS_CODEPAGE_771 is not set

+# CONFIG_FATFS_CODEPAGE_775 is not set

+# CONFIG_FATFS_CODEPAGE_850 is not set

+# CONFIG_FATFS_CODEPAGE_852 is not set

+# CONFIG_FATFS_CODEPAGE_855 is not set

+# CONFIG_FATFS_CODEPAGE_857 is not set

+# CONFIG_FATFS_CODEPAGE_860 is not set

+# CONFIG_FATFS_CODEPAGE_861 is not set

+# CONFIG_FATFS_CODEPAGE_862 is not set

+# CONFIG_FATFS_CODEPAGE_863 is not set

+# CONFIG_FATFS_CODEPAGE_864 is not set

+# CONFIG_FATFS_CODEPAGE_865 is not set

+# CONFIG_FATFS_CODEPAGE_866 is not set

+# CONFIG_FATFS_CODEPAGE_869 is not set

+# CONFIG_FATFS_CODEPAGE_932 is not set

+# CONFIG_FATFS_CODEPAGE_936 is not set

+# CONFIG_FATFS_CODEPAGE_949 is not set

+# CONFIG_FATFS_CODEPAGE_950 is not set

+CONFIG_FATFS_CODEPAGE=437

+CONFIG_FATFS_LFN_NONE=y

+# CONFIG_FATFS_LFN_HEAP is not set

+# CONFIG_FATFS_LFN_STACK is not set

+CONFIG_FATFS_FS_LOCK=0

+CONFIG_FATFS_TIMEOUT_MS=10000

+CONFIG_FATFS_PER_FILE_CACHE=y

+# CONFIG_FATFS_USE_FASTSEEK is not set

+# end of FAT Filesystem support

+

+#

+# Modbus configuration

+#

+# CONFIG_FMB_COMM_MODE_TCP_EN is not set

+# CONFIG_FMB_COMM_MODE_RTU_EN is not set

+CONFIG_FMB_COMM_MODE_ASCII_EN=y

+CONFIG_FMB_MASTER_TIMEOUT_MS_RESPOND=150

+CONFIG_FMB_MASTER_DELAY_MS_CONVERT=200

+CONFIG_FMB_QUEUE_LENGTH=20

+CONFIG_FMB_PORT_TASK_STACK_SIZE=4096

+CONFIG_FMB_SERIAL_BUF_SIZE=256

+CONFIG_FMB_SERIAL_ASCII_BITS_PER_SYMB=8

+CONFIG_FMB_SERIAL_ASCII_TIMEOUT_RESPOND_MS=1000

+CONFIG_FMB_PORT_TASK_PRIO=10

+CONFIG_FMB_PORT_TASK_AFFINITY=0x7FFFFFFF

+CONFIG_FMB_CONTROLLER_SLAVE_ID_SUPPORT=y

+CONFIG_FMB_CONTROLLER_SLAVE_ID=0x00112233

+CONFIG_FMB_CONTROLLER_NOTIFY_TIMEOUT=20

+CONFIG_FMB_CONTROLLER_NOTIFY_QUEUE_SIZE=20

+CONFIG_FMB_CONTROLLER_STACK_SIZE=4096

+CONFIG_FMB_EVENT_QUEUE_TIMEOUT=20

+# CONFIG_FMB_TIMER_PORT_ENABLED is not set

+CONFIG_FMB_TIMER_GROUP=0

+CONFIG_FMB_TIMER_INDEX=0

+CONFIG_FMB_MASTER_TIMER_GROUP=0

+CONFIG_FMB_MASTER_TIMER_INDEX=0

+# CONFIG_FMB_TIMER_ISR_IN_IRAM is not set

+# end of Modbus configuration

+

+#

+# FreeRTOS

+#

+CONFIG_FREERTOS_UNICORE=y

+CONFIG_FREERTOS_NO_AFFINITY=0x7FFFFFFF

+CONFIG_FREERTOS_TICK_SUPPORT_SYSTIMER=y

+CONFIG_FREERTOS_CORETIMER_SYSTIMER_LVL1=y

+# CONFIG_FREERTOS_CORETIMER_SYSTIMER_LVL3 is not set

+CONFIG_FREERTOS_SYSTICK_USES_SYSTIMER=y

+CONFIG_FREERTOS_OPTIMIZED_SCHEDULER=y

+CONFIG_FREERTOS_HZ=1000

+CONFIG_FREERTOS_ASSERT_ON_UNTESTED_FUNCTION=y

+# CONFIG_FREERTOS_CHECK_STACKOVERFLOW_NONE is not set

+# CONFIG_FREERTOS_CHECK_STACKOVERFLOW_PTRVAL is not set

+CONFIG_FREERTOS_CHECK_STACKOVERFLOW_CANARY=y

+# CONFIG_FREERTOS_WATCHPOINT_END_OF_STACK is not set

+# CONFIG_FREERTOS_INTERRUPT_BACKTRACE is not set

+CONFIG_FREERTOS_THREAD_LOCAL_STORAGE_POINTERS=1

+CONFIG_FREERTOS_ASSERT_FAIL_ABORT=y

+# CONFIG_FREERTOS_ASSERT_FAIL_PRINT_CONTINUE is not set

+# CONFIG_FREERTOS_ASSERT_DISABLE is not set

+CONFIG_FREERTOS_IDLE_TASK_STACKSIZE=1536

+CONFIG_FREERTOS_ISR_STACKSIZE=1536

+# CONFIG_FREERTOS_LEGACY_HOOKS is not set

+CONFIG_FREERTOS_MAX_TASK_NAME_LEN=16

+CONFIG_FREERTOS_SUPPORT_STATIC_ALLOCATION=y

+# CONFIG_FREERTOS_ENABLE_STATIC_TASK_CLEAN_UP is not set

+CONFIG_FREERTOS_TIMER_TASK_PRIORITY=1

+CONFIG_FREERTOS_TIMER_TASK_STACK_DEPTH=2048

+CONFIG_FREERTOS_TIMER_QUEUE_LENGTH=10

+CONFIG_FREERTOS_QUEUE_REGISTRY_SIZE=0

+# CONFIG_FREERTOS_USE_TRACE_FACILITY is not set

+# CONFIG_FREERTOS_GENERATE_RUN_TIME_STATS is not set

+CONFIG_FREERTOS_CHECK_MUTEX_GIVEN_BY_OWNER=y

+# CONFIG_FREERTOS_CHECK_PORT_CRITICAL_COMPLIANCE is not set

+# CONFIG_FREERTOS_PLACE_FUNCTIONS_INTO_FLASH is not set

+CONFIG_FREERTOS_ENABLE_TASK_SNAPSHOT=y

+# CONFIG_FREERTOS_PLACE_SNAPSHOT_FUNS_INTO_FLASH is not set

+# end of FreeRTOS

+

+#

+# Hardware Abstraction Layer (HAL) and Low Level (LL)

+#

+CONFIG_HAL_ASSERTION_EQUALS_SYSTEM=y

+# CONFIG_HAL_ASSERTION_DISABLE is not set

+# CONFIG_HAL_ASSERTION_SILIENT is not set

+# CONFIG_HAL_ASSERTION_ENABLE is not set

+CONFIG_HAL_DEFAULT_ASSERTION_LEVEL=2

+# end of Hardware Abstraction Layer (HAL) and Low Level (LL)

+

+#

+# Heap memory debugging

+#

+CONFIG_HEAP_POISONING_DISABLED=y

+# CONFIG_HEAP_POISONING_LIGHT is not set

+# CONFIG_HEAP_POISONING_COMPREHENSIVE is not set

+CONFIG_HEAP_TRACING_OFF=y

+# CONFIG_HEAP_TRACING_STANDALONE is not set

+# CONFIG_HEAP_TRACING_TOHOST is not set

+# CONFIG_HEAP_ABORT_WHEN_ALLOCATION_FAILS is not set

+# end of Heap memory debugging

+

+#

+# jsmn

+#

+# CONFIG_JSMN_PARENT_LINKS is not set

+# CONFIG_JSMN_STRICT is not set

+# end of jsmn

+

+#

+# libsodium

+#

+# end of libsodium

+

+#

+# Log output

+#

+# CONFIG_LOG_DEFAULT_LEVEL_NONE is not set

+# CONFIG_LOG_DEFAULT_LEVEL_ERROR is not set

+# CONFIG_LOG_DEFAULT_LEVEL_WARN is not set

+CONFIG_LOG_DEFAULT_LEVEL_INFO=y

+# CONFIG_LOG_DEFAULT_LEVEL_DEBUG is not set

+# CONFIG_LOG_DEFAULT_LEVEL_VERBOSE is not set

+CONFIG_LOG_DEFAULT_LEVEL=3

+CONFIG_LOG_MAXIMUM_EQUALS_DEFAULT=y

+# CONFIG_LOG_MAXIMUM_LEVEL_DEBUG is not set

+# CONFIG_LOG_MAXIMUM_LEVEL_VERBOSE is not set

+CONFIG_LOG_MAXIMUM_LEVEL=3

+CONFIG_LOG_COLORS=y

+CONFIG_LOG_TIMESTAMP_SOURCE_RTOS=y

+# CONFIG_LOG_TIMESTAMP_SOURCE_SYSTEM is not set

+# end of Log output

+

+#

+# LWIP

+#

+CONFIG_LWIP_LOCAL_HOSTNAME="espressif"

+# CONFIG_LWIP_NETIF_API is not set

+# CONFIG_LWIP_TCPIP_CORE_LOCKING is not set

+CONFIG_LWIP_DNS_SUPPORT_MDNS_QUERIES=y

+# CONFIG_LWIP_L2_TO_L3_COPY is not set

+CONFIG_LWIP_IRAM_OPTIMIZATION=y

+CONFIG_LWIP_TIMERS_ONDEMAND=y

+CONFIG_LWIP_MAX_SOCKETS=10

+# CONFIG_LWIP_USE_ONLY_LWIP_SELECT is not set

+# CONFIG_LWIP_SO_LINGER is not set

+CONFIG_LWIP_SO_REUSE=y

+CONFIG_LWIP_SO_REUSE_RXTOALL=y

+# CONFIG_LWIP_SO_RCVBUF is not set

+# CONFIG_LWIP_NETBUF_RECVINFO is not set

+CONFIG_LWIP_IP4_FRAG=y

+CONFIG_LWIP_IP6_FRAG=y

+# CONFIG_LWIP_IP4_REASSEMBLY is not set

+# CONFIG_LWIP_IP6_REASSEMBLY is not set

+# CONFIG_LWIP_IP_FORWARD is not set

+# CONFIG_LWIP_STATS is not set

+# CONFIG_LWIP_ETHARP_TRUST_IP_MAC is not set

+CONFIG_LWIP_ESP_GRATUITOUS_ARP=y

+CONFIG_LWIP_GARP_TMR_INTERVAL=60

+CONFIG_LWIP_TCPIP_RECVMBOX_SIZE=32

+CONFIG_LWIP_DHCP_DOES_ARP_CHECK=y

+# CONFIG_LWIP_DHCP_DISABLE_CLIENT_ID is not set

+CONFIG_LWIP_DHCP_DISABLE_VENDOR_CLASS_ID=y

+# CONFIG_LWIP_DHCP_RESTORE_LAST_IP is not set

+CONFIG_LWIP_DHCP_OPTIONS_LEN=68

+

+#

+# DHCP server

+#

+CONFIG_LWIP_DHCPS=y

+CONFIG_LWIP_DHCPS_LEASE_UNIT=60

+CONFIG_LWIP_DHCPS_MAX_STATION_NUM=8

+# end of DHCP server

+

+# CONFIG_LWIP_AUTOIP is not set

+CONFIG_LWIP_IPV6=y

+# CONFIG_LWIP_IPV6_AUTOCONFIG is not set

+CONFIG_LWIP_IPV6_NUM_ADDRESSES=3

+# CONFIG_LWIP_IPV6_FORWARD is not set

+# CONFIG_LWIP_NETIF_STATUS_CALLBACK is not set

+CONFIG_LWIP_NETIF_LOOPBACK=y

+CONFIG_LWIP_LOOPBACK_MAX_PBUFS=8

+

+#

+# TCP

+#

+CONFIG_LWIP_MAX_ACTIVE_TCP=16

+CONFIG_LWIP_MAX_LISTENING_TCP=16

+CONFIG_LWIP_TCP_HIGH_SPEED_RETRANSMISSION=y

+CONFIG_LWIP_TCP_MAXRTX=12

+CONFIG_LWIP_TCP_SYNMAXRTX=12

+CONFIG_LWIP_TCP_MSS=1440

+CONFIG_LWIP_TCP_TMR_INTERVAL=250

+CONFIG_LWIP_TCP_MSL=60000

+CONFIG_LWIP_TCP_SND_BUF_DEFAULT=5744

+CONFIG_LWIP_TCP_WND_DEFAULT=5744

+CONFIG_LWIP_TCP_RECVMBOX_SIZE=6

+CONFIG_LWIP_TCP_QUEUE_OOSEQ=y

+# CONFIG_LWIP_TCP_SACK_OUT is not set

+# CONFIG_LWIP_TCP_KEEP_CONNECTION_WHEN_IP_CHANGES is not set

+CONFIG_LWIP_TCP_OVERSIZE_MSS=y

+# CONFIG_LWIP_TCP_OVERSIZE_QUARTER_MSS is not set

+# CONFIG_LWIP_TCP_OVERSIZE_DISABLE is not set

+CONFIG_LWIP_TCP_RTO_TIME=1500

+# end of TCP

+

+#

+# UDP

+#

+CONFIG_LWIP_MAX_UDP_PCBS=16

+CONFIG_LWIP_UDP_RECVMBOX_SIZE=6

+# end of UDP

+

+#

+# Checksums

+#

+# CONFIG_LWIP_CHECKSUM_CHECK_IP is not set

+# CONFIG_LWIP_CHECKSUM_CHECK_UDP is not set

+CONFIG_LWIP_CHECKSUM_CHECK_ICMP=y

+# end of Checksums

+

+CONFIG_LWIP_TCPIP_TASK_STACK_SIZE=3072

+CONFIG_LWIP_TCPIP_TASK_AFFINITY_NO_AFFINITY=y

+# CONFIG_LWIP_TCPIP_TASK_AFFINITY_CPU0 is not set

+CONFIG_LWIP_TCPIP_TASK_AFFINITY=0x7FFFFFFF

+# CONFIG_LWIP_PPP_SUPPORT is not set

+CONFIG_LWIP_IPV6_MEMP_NUM_ND6_QUEUE=3

+CONFIG_LWIP_IPV6_ND6_NUM_NEIGHBORS=5

+# CONFIG_LWIP_SLIP_SUPPORT is not set

+

+#

+# ICMP

+#

+CONFIG_LWIP_ICMP=y

+# CONFIG_LWIP_MULTICAST_PING is not set

+# CONFIG_LWIP_BROADCAST_PING is not set

+# end of ICMP

+

+#

+# LWIP RAW API

+#

+CONFIG_LWIP_MAX_RAW_PCBS=16

+# end of LWIP RAW API

+

+#

+# SNTP

+#

+CONFIG_LWIP_SNTP_MAX_SERVERS=1

+# CONFIG_LWIP_DHCP_GET_NTP_SRV is not set

+CONFIG_LWIP_SNTP_UPDATE_DELAY=3600000

+# end of SNTP

+

+CONFIG_LWIP_ESP_LWIP_ASSERT=y

+

+#

+# Hooks

+#

+# CONFIG_LWIP_HOOK_TCP_ISN_NONE is not set

+CONFIG_LWIP_HOOK_TCP_ISN_DEFAULT=y

+# CONFIG_LWIP_HOOK_TCP_ISN_CUSTOM is not set

+CONFIG_LWIP_HOOK_IP6_ROUTE_NONE=y

+# CONFIG_LWIP_HOOK_IP6_ROUTE_DEFAULT is not set

+# CONFIG_LWIP_HOOK_IP6_ROUTE_CUSTOM is not set

+CONFIG_LWIP_HOOK_ND6_GET_GW_NONE=y

+# CONFIG_LWIP_HOOK_ND6_GET_GW_DEFAULT is not set

+# CONFIG_LWIP_HOOK_ND6_GET_GW_CUSTOM is not set

+CONFIG_LWIP_HOOK_NETCONN_EXT_RESOLVE_NONE=y

+# CONFIG_LWIP_HOOK_NETCONN_EXT_RESOLVE_DEFAULT is not set

+# CONFIG_LWIP_HOOK_NETCONN_EXT_RESOLVE_CUSTOM is not set

+# end of Hooks

+

+# CONFIG_LWIP_DEBUG is not set

+# end of LWIP

+

+#

+# mbedTLS

+#

+CONFIG_MBEDTLS_INTERNAL_MEM_ALLOC=y

+# CONFIG_MBEDTLS_DEFAULT_MEM_ALLOC is not set

+# CONFIG_MBEDTLS_CUSTOM_MEM_ALLOC is not set

+CONFIG_MBEDTLS_ASYMMETRIC_CONTENT_LEN=y

+CONFIG_MBEDTLS_SSL_IN_CONTENT_LEN=16384

+CONFIG_MBEDTLS_SSL_OUT_CONTENT_LEN=4096

+# CONFIG_MBEDTLS_DYNAMIC_BUFFER is not set

+# CONFIG_MBEDTLS_DEBUG is not set

+

+#

+# mbedTLS v2.28.x related

+#

+# CONFIG_MBEDTLS_SSL_VARIABLE_BUFFER_LENGTH is not set

+# CONFIG_MBEDTLS_X509_TRUSTED_CERT_CALLBACK is not set

+# CONFIG_MBEDTLS_SSL_CONTEXT_SERIALIZATION is not set

+CONFIG_MBEDTLS_SSL_KEEP_PEER_CERTIFICATE=y

+# end of mbedTLS v2.28.x related

+

+#

+# Certificate Bundle

+#

+CONFIG_MBEDTLS_CERTIFICATE_BUNDLE=y

+CONFIG_MBEDTLS_CERTIFICATE_BUNDLE_DEFAULT_FULL=y

+# CONFIG_MBEDTLS_CERTIFICATE_BUNDLE_DEFAULT_CMN is not set

+# CONFIG_MBEDTLS_CERTIFICATE_BUNDLE_DEFAULT_NONE is not set

+# CONFIG_MBEDTLS_CUSTOM_CERTIFICATE_BUNDLE is not set

+CONFIG_MBEDTLS_CERTIFICATE_BUNDLE_MAX_CERTS=200

+# end of Certificate Bundle

+

+# CONFIG_MBEDTLS_ECP_RESTARTABLE is not set

+# CONFIG_MBEDTLS_CMAC_C is not set

+CONFIG_MBEDTLS_HARDWARE_AES=y

+CONFIG_MBEDTLS_AES_USE_INTERRUPT=y

+CONFIG_MBEDTLS_HARDWARE_MPI=y

+CONFIG_MBEDTLS_HARDWARE_SHA=y

+CONFIG_MBEDTLS_ROM_MD5=y

+# CONFIG_MBEDTLS_ATCA_HW_ECDSA_SIGN is not set

+# CONFIG_MBEDTLS_ATCA_HW_ECDSA_VERIFY is not set

+CONFIG_MBEDTLS_HAVE_TIME=y

+# CONFIG_MBEDTLS_HAVE_TIME_DATE is not set

+CONFIG_MBEDTLS_ECDSA_DETERMINISTIC=y

+CONFIG_MBEDTLS_SHA512_C=y

+CONFIG_MBEDTLS_TLS_SERVER_AND_CLIENT=y

+# CONFIG_MBEDTLS_TLS_SERVER_ONLY is not set

+# CONFIG_MBEDTLS_TLS_CLIENT_ONLY is not set

+# CONFIG_MBEDTLS_TLS_DISABLED is not set

+CONFIG_MBEDTLS_TLS_SERVER=y

+CONFIG_MBEDTLS_TLS_CLIENT=y

+CONFIG_MBEDTLS_TLS_ENABLED=y

+

+#

+# TLS Key Exchange Methods

+#

+# CONFIG_MBEDTLS_PSK_MODES is not set

+CONFIG_MBEDTLS_KEY_EXCHANGE_RSA=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_DHE_RSA=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_ELLIPTIC_CURVE=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_ECDHE_RSA=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_ECDHE_ECDSA=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_ECDH_ECDSA=y

+CONFIG_MBEDTLS_KEY_EXCHANGE_ECDH_RSA=y

+# end of TLS Key Exchange Methods

+

+CONFIG_MBEDTLS_SSL_RENEGOTIATION=y

+# CONFIG_MBEDTLS_SSL_PROTO_SSL3 is not set

+CONFIG_MBEDTLS_SSL_PROTO_TLS1=y

+CONFIG_MBEDTLS_SSL_PROTO_TLS1_1=y

+CONFIG_MBEDTLS_SSL_PROTO_TLS1_2=y

+# CONFIG_MBEDTLS_SSL_PROTO_GMTSSL1_1 is not set

+# CONFIG_MBEDTLS_SSL_PROTO_DTLS is not set

+CONFIG_MBEDTLS_SSL_ALPN=y

+CONFIG_MBEDTLS_CLIENT_SSL_SESSION_TICKETS=y

+CONFIG_MBEDTLS_X509_CHECK_KEY_USAGE=y

+CONFIG_MBEDTLS_X509_CHECK_EXTENDED_KEY_USAGE=y

+CONFIG_MBEDTLS_SERVER_SSL_SESSION_TICKETS=y

+

+#

+# Symmetric Ciphers

+#

+CONFIG_MBEDTLS_AES_C=y

+# CONFIG_MBEDTLS_CAMELLIA_C is not set

+# CONFIG_MBEDTLS_DES_C is not set

+CONFIG_MBEDTLS_RC4_DISABLED=y

+# CONFIG_MBEDTLS_RC4_ENABLED_NO_DEFAULT is not set

+# CONFIG_MBEDTLS_RC4_ENABLED is not set

+# CONFIG_MBEDTLS_BLOWFISH_C is not set

+# CONFIG_MBEDTLS_XTEA_C is not set

+CONFIG_MBEDTLS_CCM_C=y

+CONFIG_MBEDTLS_GCM_C=y

+# CONFIG_MBEDTLS_NIST_KW_C is not set

+# end of Symmetric Ciphers

+

+# CONFIG_MBEDTLS_RIPEMD160_C is not set

+

+#

+# Certificates

+#

+CONFIG_MBEDTLS_PEM_PARSE_C=y

+CONFIG_MBEDTLS_PEM_WRITE_C=y

+CONFIG_MBEDTLS_X509_CRL_PARSE_C=y

+CONFIG_MBEDTLS_X509_CSR_PARSE_C=y

+# end of Certificates

+

+CONFIG_MBEDTLS_ECP_C=y

+CONFIG_MBEDTLS_ECDH_C=y

+CONFIG_MBEDTLS_ECDSA_C=y

+# CONFIG_MBEDTLS_ECJPAKE_C is not set

+CONFIG_MBEDTLS_ECP_DP_SECP192R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP224R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP256R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP384R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP521R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP192K1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP224K1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_SECP256K1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_BP256R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_BP384R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_BP512R1_ENABLED=y

+CONFIG_MBEDTLS_ECP_DP_CURVE25519_ENABLED=y

+CONFIG_MBEDTLS_ECP_NIST_OPTIM=y

+# CONFIG_MBEDTLS_POLY1305_C is not set

+# CONFIG_MBEDTLS_CHACHA20_C is not set

+# CONFIG_MBEDTLS_HKDF_C is not set

+# CONFIG_MBEDTLS_THREADING_C is not set

+CONFIG_MBEDTLS_LARGE_KEY_SOFTWARE_MPI=y

+# CONFIG_MBEDTLS_SECURITY_RISKS is not set

+# end of mbedTLS

+

+#

+# mDNS

+#

+CONFIG_MDNS_MAX_SERVICES=10

+CONFIG_MDNS_TASK_PRIORITY=1

+CONFIG_MDNS_TASK_STACK_SIZE=4096

+# CONFIG_MDNS_TASK_AFFINITY_NO_AFFINITY is not set

+CONFIG_MDNS_TASK_AFFINITY_CPU0=y

+CONFIG_MDNS_TASK_AFFINITY=0x0

+CONFIG_MDNS_SERVICE_ADD_TIMEOUT_MS=2000

+# CONFIG_MDNS_STRICT_MODE is not set

+CONFIG_MDNS_TIMER_PERIOD_MS=100

+# CONFIG_MDNS_NETWORKING_SOCKET is not set

+CONFIG_MDNS_MULTIPLE_INSTANCE=y

+# end of mDNS

+

+#

+# ESP-MQTT Configurations

+#

+CONFIG_MQTT_PROTOCOL_311=y

+# CONFIG_MQTT_TRANSPORT_SSL is not set

+# CONFIG_MQTT_TRANSPORT_WEBSOCKET is not set

+# CONFIG_MQTT_MSG_ID_INCREMENTAL is not set

+# CONFIG_MQTT_SKIP_PUBLISH_IF_DISCONNECTED is not set

+# CONFIG_MQTT_REPORT_DELETED_MESSAGES is not set

+# CONFIG_MQTT_USE_CUSTOM_CONFIG is not set

+# CONFIG_MQTT_TASK_CORE_SELECTION_ENABLED is not set

+# CONFIG_MQTT_CUSTOM_OUTBOX is not set

+# end of ESP-MQTT Configurations

+

+#

+# Newlib

+#

+CONFIG_NEWLIB_STDOUT_LINE_ENDING_CRLF=y

+# CONFIG_NEWLIB_STDOUT_LINE_ENDING_LF is not set

+# CONFIG_NEWLIB_STDOUT_LINE_ENDING_CR is not set

+# CONFIG_NEWLIB_STDIN_LINE_ENDING_CRLF is not set

+# CONFIG_NEWLIB_STDIN_LINE_ENDING_LF is not set

+CONFIG_NEWLIB_STDIN_LINE_ENDING_CR=y

+# CONFIG_NEWLIB_NANO_FORMAT is not set

+# end of Newlib

+

+#

+# NVS

+#

+# CONFIG_NVS_ASSERT_ERROR_CHECK is not set

+# end of NVS

+

+#

+# OpenSSL

+#

+# CONFIG_OPENSSL_DEBUG is not set

+CONFIG_OPENSSL_ERROR_STACK=y

+# CONFIG_OPENSSL_ASSERT_DO_NOTHING is not set

+CONFIG_OPENSSL_ASSERT_EXIT=y

+# end of OpenSSL

+

+#

+# OpenThread

+#

+# CONFIG_OPENTHREAD_ENABLED is not set

+# end of OpenThread

+

+#

+# PThreads

+#

+CONFIG_PTHREAD_TASK_PRIO_DEFAULT=5

+CONFIG_PTHREAD_TASK_STACK_SIZE_DEFAULT=3072

+CONFIG_PTHREAD_STACK_MIN=768

+CONFIG_PTHREAD_TASK_CORE_DEFAULT=-1

+CONFIG_PTHREAD_TASK_NAME_DEFAULT="pthread"

+# end of PThreads

+

+#

+# SPI Flash driver

+#

+# CONFIG_SPI_FLASH_VERIFY_WRITE is not set

+# CONFIG_SPI_FLASH_ENABLE_COUNTERS is not set

+CONFIG_SPI_FLASH_ROM_DRIVER_PATCH=y

+# CONFIG_SPI_FLASH_ROM_IMPL is not set

+CONFIG_SPI_FLASH_DANGEROUS_WRITE_ABORTS=y

+# CONFIG_SPI_FLASH_DANGEROUS_WRITE_FAILS is not set

+# CONFIG_SPI_FLASH_DANGEROUS_WRITE_ALLOWED is not set

+# CONFIG_SPI_FLASH_USE_LEGACY_IMPL is not set

+# CONFIG_SPI_FLASH_SHARE_SPI1_BUS is not set

+# CONFIG_SPI_FLASH_BYPASS_BLOCK_ERASE is not set

+CONFIG_SPI_FLASH_YIELD_DURING_ERASE=y

+CONFIG_SPI_FLASH_ERASE_YIELD_DURATION_MS=20

+CONFIG_SPI_FLASH_ERASE_YIELD_TICKS=1

+# CONFIG_SPI_FLASH_AUTO_SUSPEND is not set

+CONFIG_SPI_FLASH_WRITE_CHUNK_SIZE=8192

+# CONFIG_SPI_FLASH_SIZE_OVERRIDE is not set

+# CONFIG_SPI_FLASH_CHECK_ERASE_TIMEOUT_DISABLED is not set

+# CONFIG_SPI_FLASH_OVERRIDE_CHIP_DRIVER_LIST is not set

+

+#

+# Auto-detect flash chips

+#

+CONFIG_SPI_FLASH_SUPPORT_ISSI_CHIP=y

+CONFIG_SPI_FLASH_SUPPORT_MXIC_CHIP=y

+CONFIG_SPI_FLASH_SUPPORT_GD_CHIP=y

+CONFIG_SPI_FLASH_SUPPORT_WINBOND_CHIP=y

+CONFIG_SPI_FLASH_SUPPORT_BOYA_CHIP=y

+CONFIG_SPI_FLASH_SUPPORT_TH_CHIP=y

+# end of Auto-detect flash chips

+

+CONFIG_SPI_FLASH_ENABLE_ENCRYPTED_READ_WRITE=y

+# end of SPI Flash driver

+

+#

+# SPIFFS Configuration

+#

+CONFIG_SPIFFS_MAX_PARTITIONS=3

+

+#

+# SPIFFS Cache Configuration

+#

+CONFIG_SPIFFS_CACHE=y

+CONFIG_SPIFFS_CACHE_WR=y

+# CONFIG_SPIFFS_CACHE_STATS is not set

+# end of SPIFFS Cache Configuration

+

+CONFIG_SPIFFS_PAGE_CHECK=y

+CONFIG_SPIFFS_GC_MAX_RUNS=10

+# CONFIG_SPIFFS_GC_STATS is not set

+CONFIG_SPIFFS_PAGE_SIZE=256

+CONFIG_SPIFFS_OBJ_NAME_LEN=32

+# CONFIG_SPIFFS_FOLLOW_SYMLINKS is not set

+CONFIG_SPIFFS_USE_MAGIC=y

+CONFIG_SPIFFS_USE_MAGIC_LENGTH=y

+CONFIG_SPIFFS_META_LENGTH=4

+CONFIG_SPIFFS_USE_MTIME=y

+

+#

+# Debug Configuration

+#

+# CONFIG_SPIFFS_DBG is not set

+# CONFIG_SPIFFS_API_DBG is not set

+# CONFIG_SPIFFS_GC_DBG is not set

+# CONFIG_SPIFFS_CACHE_DBG is not set

+# CONFIG_SPIFFS_CHECK_DBG is not set

+# CONFIG_SPIFFS_TEST_VISUALISATION is not set

+# end of Debug Configuration

+# end of SPIFFS Configuration

+

+#

+# TCP Transport

+#

+

+#

+# Websocket

+#

+CONFIG_WS_TRANSPORT=y

+CONFIG_WS_BUFFER_SIZE=1024

+# end of Websocket

+# end of TCP Transport

+

+#

+# Unity unit testing library

+#

+CONFIG_UNITY_ENABLE_FLOAT=y

+CONFIG_UNITY_ENABLE_DOUBLE=y

+# CONFIG_UNITY_ENABLE_64BIT is not set

+# CONFIG_UNITY_ENABLE_COLOR is not set

+CONFIG_UNITY_ENABLE_IDF_TEST_RUNNER=y

+# CONFIG_UNITY_ENABLE_FIXTURE is not set

+# CONFIG_UNITY_ENABLE_BACKTRACE_ON_FAIL is not set

+# end of Unity unit testing library

+

+#

+# Virtual file system

+#

+CONFIG_VFS_SUPPORT_IO=y

+CONFIG_VFS_SUPPORT_DIR=y

+CONFIG_VFS_SUPPORT_SELECT=y

+CONFIG_VFS_SUPPRESS_SELECT_DEBUG_OUTPUT=y

+CONFIG_VFS_SUPPORT_TERMIOS=y

+

+#

+# Host File System I/O (Semihosting)

+#

+CONFIG_VFS_SEMIHOSTFS_MAX_MOUNT_POINTS=1

+# end of Host File System I/O (Semihosting)

+# end of Virtual file system

+

+#

+# Wear Levelling

+#

+# CONFIG_WL_SECTOR_SIZE_512 is not set

+CONFIG_WL_SECTOR_SIZE_4096=y

+CONFIG_WL_SECTOR_SIZE=4096

+# end of Wear Levelling

+

+#

+# Wi-Fi Provisioning Manager

+#

+CONFIG_WIFI_PROV_SCAN_MAX_ENTRIES=16

+CONFIG_WIFI_PROV_AUTOSTOP_TIMEOUT=30

+CONFIG_WIFI_PROV_BLE_FORCE_ENCRYPTION=y

+# end of Wi-Fi Provisioning Manager

+

+#

+# Supplicant

+#

+CONFIG_WPA_MBEDTLS_CRYPTO=y

+# CONFIG_WPA_WAPI_PSK is not set